x86-Prozessor

x86 ist die Abkürzung einer Mikroprozessor-Architektur und der damit verbundenen Befehlssätze, welche unter anderem von den Chip-Herstellern Intel und AMD entwickelt werden.

Die x86-Architektur ist nach den Prozessoren der 8086/8088-Reihe benannt, mit der sie 1978 eingeführt wurde. Die ersten Nachfolgeprozessoren wurden später mit 80186, 80286 usw. benannt. Da sich Ziffernkombinationen nicht markenrechtlich schützen lassen, gingen Intel und die meisten Mitbewerber nach Einführung des Intel 80486 dazu über, Wortmarken wie Pentium oder Celeron zu verwenden, aber das alte Nummernschema blieb als Name der ganzen Familie erhalten. Intel selbst nennt die Architektur heute IA-32 als Abkürzung für „Intel Architecture with 32-bit.“

Geschichte

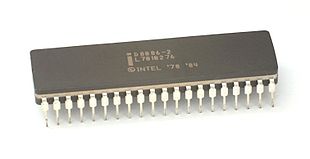

Die x86-Architektur wurde 1978 mit Intels erster 16-Bit-CPU, dem 8086, eingeführt, der die älteren 8-Bit-Prozessoren 8080 und 8085 ablösen sollte. Obwohl der 8086 anfangs nicht sonderlich erfolgreich war, stellte IBM 1981 den ersten PC vor, der eine abgespeckte Variante des 8086, den 8088, als CPU verwendete. Durch den enormen Erfolg des IBM-PC und seinen zahlreichen Nachbauten, den sogenannten IBM-Kompatiblen PCs, wurde die x86-Architektur innerhalb weniger Jahre zu einer der erfolgreichsten CPU-Architekturen der Welt und ist es bis heute geblieben.

Außer Intel haben auch andere Hersteller über die Jahre x86-kompatible CPUs produziert, darunter Cyrix (heute VIA Technologies), NEC, UMC, Harris, TI, IBM, IDT und Transmeta. Der nach Intel größte Hersteller x86-kompatibler Prozessoren war und ist aber das Unternehmen AMD, das neben Intel heute zu einer treibenden Kraft bei der Weiterentwicklung des x86-Standards geworden ist.

Intel entwickelte den 8086 1978 in der Zeit der zu Ende gehenden 8-Bit-Ära. Mit dem 80386 führte Intel dann bereits 1985 die erste x86-CPU mit einer 32-Bit-Architektur ein. Heute ist diese Architektur unter dem Namen IA-32, oft auch unter der Bezeichnung i386-Architektur bekannt; sie ist sozusagen die Erweiterung der Befehlssätze von 8086 und 80286 auf 32 Bit, schließt deren Befehlssätze aber vollständig mit ein. Die 32-Bit-Ära war der bisher längste und lukrativste Abschnitt der x86-Geschichte, wobei sich IA-32 – maßgeblich unter Intels Federführung – permanent weiterentwickelte. Erst 2003 brach für x86 die 64-Bit-Ära an, diesmal aber auf Initiative von AMD. Der 64-bittige x86-Standard heißt AMD64 und wurde unter dem Namen Intel 64 auch von Intel übernommen.

Die von Intel in der Itanium-Produktlinie verwendete IA-64-Architektur hat übrigens mit IA-32 nichts zu tun. Sie ist eine Neuentwicklung, die außer einer x86-Emulation (nur in der ältesten Itanium-Baureihe) keine Spuren der x86-Technik enthält.

Liste der x86er Generationen

| Generation | erster Prozessor | Nachfolger | Jahr der Markt- einführung |

|---|---|---|---|

| 1. | Intel 8086 (und Derivate) | 1978 | |

| 1a. | Update der ersten Generation, Intel 80186 (und Derivate) | 1982 | |

| 2. | Intel 80286 | 1982 | |

| 3. | Intel 80386 (und Derivate) | 1985 | |

| 4. | Intel 80486 (und Derivate) | 1989 | |

| 5. | Pentium (und Derivate) | Nx586, Cyrix 5x86, WinChip, mP6, AMD K5 | 1993 |

| 6. | Pentium Pro (und Derivate wie Pentium II, Celeron (PII), Xeon (PII), Pentium III, Pentium M, Intel Core) | Cyrix 6x86, AMD K6, K6-2, K6-III, VIA C3, Transmeta Crusoe | 1995 |

| 7. | Athlon (K7) (und Derivate) | Pentium 4 (und Derivate), C7, Efficeon | 1999 |

| 8. | Opteron (K8) (und Derivate, einschließlich Athlon 64) | Xeon (Core) (Xeon-5100-Serie und Derivate, einschließlich Core 2) | 2003 |

| 9. | Intel Core i-Serie (Das i als neunter Buchstabe im Alphabet soll auf die neunte Generation hindeuten) | 2008 |

Design

Die x86-Architektur verwendet einen CISC-Befehlssatz mit variabler Instruktionslänge. Speicherzugriffe in Wortgröße sind auch auf nicht Wort-ausgerichtete Speicheradressen erlaubt. Wörter werden in Little-Endian-Richtung gespeichert. Leichte Portierbarkeit von Intel-8085-Assemblercode war eine treibende Kraft der Architekturentwicklung. Dies bedingte einige nicht optimale und im Nachhinein problematische Designentscheidungen.

Heutige x86-Prozessoren sind hybride CISC/RISC-Prozessoren, denn sie übersetzen den x86-Befehlssatz zunächst in RISC-Mikro-Instruktionen konstanter Länge, auf die moderne mikro-architektonische Optimierungen angewendet werden können. Die Übergabe erfolgt zunächst an sogenannte Reservierungsstationen, das heißt an kleine Puffer, die den verschiedenen Rechenwerken vorgeschaltet sind. Der erste hybride x86-Prozessor war der Pentium Pro.

Real Mode

Die Intel 8086 und 8088 hatten 14 16-Bit-Register. Vier von ihnen (AX, BX, CX, DX) waren Mehrzweck-Register. Zusätzlich hatte jedes noch eine Sonderfunktion:

- AX (engl. accumulator register) diente als bevorzugtes Ziel für Rechenoperationen

- BX (engl. base register) diente zur Adressierung der Anfangsadresse einer Datenstruktur

- CX (engl. count register) diente als Zähler für Schleifen (loop-Instruktion) und Verschiebeoperationen

- DX (engl. data register) diente als Datenregister für den zweiten Operanden.

Auf jedes Register konnte mittels zwei separater Bytes zugegriffen werden (das hohe Byte in BX unter dem Namen BH, das niederwertige Byte als BL). Von den zwei Zeigerregistern zeigt SP („StackPointer“) auf das oberste Element des Stacks und BP („BasePointer“) kann auf einen anderen Platz im Stack oder Speicher zeigen (häufig wird BP als Zeiger auf einen Funktionsrahmen verwendet). Die beiden Index-Register SI („SourceIndex“) und DI („DestinationIndex“) können für Blockoperationen oder zusammen mit SP oder BP als Index in einem Array benutzt werden. Zusätzlich gibt es die vier Segmentregister CS („CodeSegment“), DS („DataSegment“), SS („StackSegment“) und ES („ExtraSegment“), mit denen jeweils die Basisadresse für ein 64 kB großes Speichersegment festgelegt wird. Außerdem gibt es das Flag-Register, das Flags wie carry, overflow, zero usw. enthalten kann, und den Instruction Pointer (IP), der auf die gegenwärtige Instruktion zeigt.

Im Real Mode ist der Speicherzugriff „segmentiert“. Dies geschieht, indem die Segmentadresse um 4 Bit nach links geschoben wird und ein Offset addiert wird, so dass eine 20-Bit-Adresse entsteht. Der gesamte Adressraum im Real Mode ist also 220 Byte (1 Megabyte), was 1978 sehr viel war. Es gibt zwei Adressierungs-Modi: near und far (engl. für nah und fern). Im Far Mode werden sowohl das Segment als auch der Offset angegeben. Im Near Mode wird nur der Offset angegeben, und das Segment wird einem Register entnommen. Für Daten ist dies DS, für Code CS und für den Stack SS. Wenn DS zum Beispiel A000h und SI 5677h ist, zeigt DS:SI auf die absolute Adresse DS × 16 + SI = A5677h.

In diesem Schema können unterschiedliche Segment/Offset-Paare auf dieselbe absolute Adresse zeigen. Wenn DS A111h und SI 4567h ist, zeigt DS:SI ebenfalls auf die obige Adresse A5677h. Das Schema sollte die Portierbarkeit von Intel-8085-Code erleichtern und hat einer ganzen Generation von Programmierern Kopfschmerzen bereitet.

Zusätzlich hatte der i8086 64 kB von 8-Bit-I/O-Adressraum (alternativ auch 32 kB mit 16 Bit) sowie einen hardwareunterstützten Stack von ebenfalls 64 kB. Nur Wörter (2 Byte) können auf dem Stack abgelegt werden. Der Stack wächst zu niedrigeren Adressen hin und SS:SP zeigt auf das zuletzt auf den Stack gelegte Wort (die niedrigste Adresse). Es gibt 256 Interrupts, die sowohl von Hardware als auch Software ausgelöst werden können. Die Interrupts können kaskadieren und benutzen den Stack, um die Rücksprungadresse zu speichern.

Protected und Enhanced Mode

Der Intel-80286-Prozessor kannte einen weiteren Arbeitsmodus, den „Protected Mode“. Durch Integration einer MMU (engl. “Memory Management Unit” für Speicherverwaltungseinheit) auf dem Chip konnten im Protected Mode bis zu 16 MB Speicher adressiert werden. Ein spezielles MMU-Register zeigt dabei auf eine Segmenttabelle im Hauptspeicher, in der die 24-Bit-Basisadressen der Segmente festgelegt wurden. Die Segmentregister dienten dann lediglich als Index in diese Segment-Tabelle. Zusätzlich konnte jedem Segment einer von vier Privilegien-Levels zugeordnet werden („Ringe“ genannt). Insgesamt bedeuteten diese Neuerungen eine Verbesserung. Allerdings war Software für den Protected Mode inkompatibel mit dem Real Mode des i8086-Prozessors.

Die Intel-80386 brachte den wahrscheinlich größten Sprung für die x86-Architektur. Mit Ausnahme des Chips „Intel 80386SX“, der nur 24-Bit-Adressierung unterstützte und einen 16-Bit-Datenbus hatte, waren alle 386er vollständig 32-Bit – Register, Instruktionen, E/A-Raum und Speicher. Bis zu 4 GB Speicher konnten angesprochen werden. Dazu wurde der Protected Mode zum „32-Bit-Enhanced-Mode“ erweitert. Wie auf dem 80286 wurden auch im Enhanced Mode die Segmentregister als Index in einer Segmenttabelle verwendet, die die Aufteilung des Speichers beschrieb. Allerdings konnten in jedem Segment 32-Bit-Offsets verwendet werden. Dies führte zum sogenannten „Flat Memory Model“, bei dem jedem Prozess nur noch ein 4-GB-Datensegment und ein 4-GB-Codesegment zur Verfügung gestellt wird. Beide Segmente beginnen ab der Adresse 0 und sind 4 GB groß. Die eigentliche Speicherverwaltung wird dann nur noch durch das ebenfalls mit dem 80386er eingeführte Paging durchgeführt, einem Mechanismus, der den gesamten Speicher in gleich große Teile (engl. Pages, also Speicherseiten) einteilt und pro Prozess eine beliebige Abbildung zwischen logischen und physischen Adressen ermöglicht, was die Realisierung von virtuellem Speicher stark vereinfacht hat. Es wurden keine neuen Mehrzweck-Register hinzugefügt. Allerdings wurden bis auf die Segmentregister alle Register auf 32 Bit verbreitert. Das erweiterte Register AX hieß fortan EAX, aus SI wurde ESI usw. Zwei neue Segmentregister namens FS und GS kamen noch hinzu.

Die grundlegende Architektur des 386er-Prozessors (auch IA-32 genannt) wurde zur Basis aller weiteren Entwicklungen in der x86-Architektur. Bis heute funktionieren alle x86-kompatiblen CPUs nach dem Prinzip des i80386.

Der bis dato separate mathematische Coprozessor 80387 wurde ab der nächsten CPU, dem „Intel 80486“, direkt in den Prozessor integriert (mit Ausnahme des 486SX, welcher keinen Coprozessor besitzt). Mit diesem Coprozessor konnten Gleitkommaberechnungen in Hardware durchgeführt werden. Ohne ihn mussten diese auf Berechnungen mit ganzen Zahlen abgebildet werden (Emulation). Nicht nur werden so recht viele Befehle pro Gleitkommaoperation benötigt, auch treten dabei häufig Schleifen und Verzweigungen auf, sodass Gleitkommaoperationen ohne den Coprozessor vergleichsweise sehr langsam ausgeführt wurden.

Register

- AX/EAX/RAX: Akkumulator

- BX/EBX/RBX: Basis

- CX/ECX/RCX: Zähler

- DX/EDX/RDX: Daten/Allzweck

- SI/ESI/RSI: Quellindex (Zeichenketten)

- DI/EDI/RDI: Zielindex (Zeichenketten)

- SP/ESP/RSP: Stapelzeiger

- BP/EBP/RBP: Stapelsegment (Anfangsadresse)

- IP/EIP/RIP: Befehlszeiger

MMX und 3DNow!

1996 führte Intel die MMX-Technologie ein (engl. Matrix Math Extensions, besonders vom Marketing aber auch häufig Multi-Media Extensions tituliert). MMX definierte 8 neue SIMD-Register von 64 Bit Breite, die allerdings denselben Speicherplatz wie die Register der Floating Point Unit (FPU) benutzten. Dies verbesserte zwar die Kompatibilität zu bestehenden Betriebssystemen, die beim Umschalten zwischen verschiedenen Anwendungen weiterhin nur die altbekannten FPU-Register sichern mussten. Aber zwischen MMX und FPU musste aufwendig umgeschaltet werden. Dazu kam, dass MMX auf Integer-Operationen beschränkt war und lange Zeit von den Compilern nicht richtig unterstützt wurde. Insbesondere Microsoft tat sich schwer, den hauseigenen Compiler wenigstens mit Unterstützung für MMX-Intrinsics auszustatten. MMX wurde daher nur relativ selten verwendet, am ehesten noch für 2D-Videobearbeitung, Bildbearbeitung, Videowiedergabe usw.

1997 erweiterte AMD den MMX-Befehlssatz um Gleitkomma-Operationen für Gleitkommazahlen einfacher Genauigkeit und nannte die so entstandene Technik 3DNow!. Dies löste zwar nicht die Compiler-Probleme, aber 3DNow! ließ sich im Unterschied zu MMX für 3D-Spiele verwenden, die auf schnelle Gleitkomma-Operationen angewiesen sind. Spieleentwickler und Hersteller von 3D-Grafikprogrammen verwendeten 3DNow!, um die Anwendungsperformance auf AMDs K6- und Athlon-Prozessoren zu verbessern.

Streaming SIMD Extensions

| Befehlssatz | Instruktionen | |

|---|---|---|

| Anzahl | Summe | |

| x86 (Basis) | 80 | 80 |

| MMX | 57 | 140 |

| SSE | 70 | 200 |

| SSE2 | 144 | 350 |

| SSE3 | 13 | 360 |

| SSSE3 | 16 | 380 |

| SSE4 | 54 | 430 |

| SSE5 | 47 | 480 |

1999 brachte Intel mit dem Pentium-III-Prozessor den SSE-Befehlssatz. Wie AMD fügte Intel hauptsächlich Gleitkomma-SIMD-Befehle hinzu. Des Weiteren schuf man für SSE eine separate Funktionseinheit auf dem Prozessor mit 8 neuen 128-Bit-Registern (XMM0 bis XMM7), die sich nicht mehr mit den Gleitkommaregistern überlagerten. Da diese neuen Register aber auch bei einem Kontextwechsel vom Betriebssystem gesichert werden müssen, wurde eine Sperre in der CPU verbaut, die erst von SSE-fähigen Betriebssystemen freigeschaltet werden muss, um die SSE-Register in Anwendungsprogrammen verfügbar zu machen.

AMD-Prozessoren unterstützten anfänglich nur die 64-Bit-Befehle der Erweiterung, welche in der MMX-Funktionseinheit arbeiten, da die separate Funktionseinheit komplett fehlte. Ein Großteil dieser Befehle arbeitet nur mit Daten vom Typ Integer, deshalb existiert auch die Bezeichnung ISSE, wobei I für Integer steht. Ab dem Athlon-XP-Prozessor wird SSE komplett unterstützt.

SSE2, von Intel 2001 mit dem Pentium 4 eingeführt, fügte erstens weitere Ganzzahlbefehle für die SSE-Register hinzu und zweitens 64-Bit-SIMD-Gleitkomma-Befehle. Erstere machten MMX fast obsolet, und letztere erlaubten auch konventionellen Compilern, SIMD-Instruktionen zu verwenden. Daher wählte AMD mit der Einführung der 64-Bit-Erweiterung SSE2 als integralen Bestandteil der AMD64-Architektur aus, sodass alle 64-Bit-x86-Prozessoren diese Erweiterung unterstützen (AMD-Prozessoren ab Athlon64).

Mit der Prescott-Revision des Pentium 4 lieferte Intel ab 2004 SSE3 aus, das hauptsächlich Speicher- und Threadmanagement-Instruktionen liefert, um die Leistung von Intels Hyper-Threading-Technologie zu steigern.

AMD beherrscht seit den Athlon-64-Prozessoren mit den Kernen Venice und San-Diego ebenfalls den Befehlssatz SSE3.

Siehe auch: SSSE3, SSE4, SSE4a und SSE5

64 Bit

Um das Jahr 2002 erreichte der Speicherausbau moderner x86-Rechner die durch die 32-Bit-Adressengröße bedingte Adressierungsgrenze der x86-Befehlssatzarchitektur von 4 GB. Zwar hatte Intel bereits mit dem Pentium Pro eine Möglichkeit eingeführt, mehr als 4 GB Arbeitsspeicher zu adressieren, allerdings war dessen Nutzung programmtechnisch aufwendig und der pro Prozess nutzbare Speicher blieb auch so nach wie vor auf maximal 4 GB beschränkt.

Intel wollte ursprünglich den Sprung auf 64 Bit mit einer neuen Prozessorarchitektur namens IA-64 vollführen, allerdings konnte sich diese nur als Nischenprodukt im Marktsegment der Server und Workstations etablieren. AMD hingegen erweiterte die 32-bit Prozessorarchitektur auf 64 Bit und nannte diese Erweiterung AMD64. Später übernahm Intel große Teile dieser Erweiterung unter der Bezeichnung EM64T, schließlich dann unter dem heute bei Intel-Produkten gebräuchlichen Namen Intel 64.

Für 64-Bit-Prozessoren, die auf der x86-Architektur beruhen, wird die Bezeichnung x86-64 oder kurz x64 verwendet.

Virtualisierung

Obwohl die Virtualisierung eines x86-Prozessors aufgrund der umfassenden Architektur aufwändig ist, gibt es mehrere Produkte, die einen virtuellen x86-Prozessor zur Verfügung stellen, darunter VMware, Hyper-V und Virtual PC oder auch Open-Source-Software wie Xen oder VirtualBox. Hardwareseitige Virtualisierung gibt es auch als Erweiterung, sie wird bei Intel „Intel VT“ (für Virtualization Technology), bei AMD „AMD Virtualization“ genannt.

Chronologie

| Prominente CPU-Typen (Endnutzerbereich) | Erstmals eingeführt | Linearer/physischer Adressraum | Bedeutende neue Eigenschaften |

|---|---|---|---|

| Intel 8086, Intel 8088 | 1978 | 16-bit / 20-bit (segmentiert) | erster x86 Mikroprozessor |

| Intel 80186, Intel 80188, NEC V20/V30 | 1982 | schnelle Speicheradress Auflösung, schnelle mul/div etc. Operationen | |

| Intel 80286 | 16-bit (30-bit virtuell) / 24-bit (segmentiert) | MMU, für den Protected Mode und einen größeren Adressraum | |

| Intel 80386, AMD Am386 | 1985 | 32-bit (46-bit virtuell) / 32-bit | 32-bit Befehlssatz, MMU mit paging |

| Intel486, AMD Am486, Cyrix III-Samuel, VIA C3-Samuel2 / VIA C3-Ezra (2001) | 1989 | RISC-ähnliches pipelining, integrierte FPU, on-chip Cache | |

| Pentium, Pentium MMX, Rise mP6 | 1993 | Superskalarität, 64-bit breiter Datenbus, schnellere FPU (Pipeline), SIMD für Integerdaten mit MMX | |

| Cyrix 6x86, Cyrix MII, Cyrix III-Joshua (2000) | 1996 | Register Renaming, Spekulative Befehlsausführung | |

| Pentium Pro, AMD K5, Nx586 (1994) | 1995 | 32-bit / 32-bit physisch (36-bit mit PAE) | µ-Instruktionsumsetzung, PAE (Pentium Pro), integrierter L2 cache (Pentium Pro), conditional move instructions (CMOV etc.) |

| AMD K6/-2/3, Pentium II/III, IDT/Centaur-C6 | 1997 | L3-cache Unterstützung, SIMD für Gleitkommadaten: AMD 3DNow!, Intel SSE | |

| Athlon, Athlon XP | 1999 | superskalare FPU, drei parallele Integer-Pipelines (bis zu drei x86 instr./clock) | |

| Pentium 4 | 2000 | lange Pipelines, optimiert für sehr hohe Taktfrequenzen, SSE2, Hyper-Threading | |

| Pentium M, VIA C7 (2005), Intel Core (2006) | 2003 | optimiert für eine geringe Verlustleistung | |

| Athlon 64, Opteron | 2003 | 64-bit / 40-bit physisch in den ersten AMD Implementierungen. | AMD64, on-die memory controller, Hypertransport |

| Pentium 4 Prescott 2M/Cedar Mill | 2004 | sehr lange Pipelines, ausgelegt für sehr hohe Taktfrequenzen, SSE3, 64-bit (nur für LGA 775 sockets) | |

| Intel Core 2 | 2006 | energieeffizient, multi-core, mittellange Pipeline, ausgelegt für geringere Taktfrequenzen als der P4, SSE4 (Penryn) | |

| AMD Phenom | 2007 | 64-bit / 48-bit physisch bei dem AMD Phenom | monolithischer Vierkerner, 128 bit FPUs, SSE4a, HyperTransport 3 oder QuickPath, integrierter Speicherkontroller, on-die L3 cache, SMT (nur bei i7), modulares Design |

| Intel Core i3, Intel Core i5, Intel Core i7 | 2008 | ||

| Intel Atom | In-order Befehlsausführung, pipelined, sehr energieeffizient | ||

| VIA Nano | Out-of-order-Befehlsausführung, superskalar, hardware encryption, sehr energieeffizient, adaptives Power Management | ||

| AMD Bobcat | 2011 | ||

| Intel Sandy Bridge | 2010 | 64-bit | Advanced Vector Extensions, AES-NI (Hardware-beschleunigte Verschlüsselung), SMT (nur bei i7), sehr modulares Design, CMT (Nur bei Bulldozer basierten Prozessoren), FMA (nur bei Bulldozer-Prozessoren) |

| AMD Bulldozer | 2011 | ||

| AMD Jaguar | 2013 | 64-bit / 40-bit physisch | AVX, AES, SSEx, sehr niedrige Leistungsaufnahme, erste HSA Features |

| Intel Haswell | 2013 | 64-bit | AVX 2, FMA3, Iris Pro Grafik |

| AMD Steamroller | 2014 | verbessertes CMT, doppelt so viele Decoder wie Bulldozer |

Hersteller

x86-kompatible Prozessoren wurden von vielen Firmen entwickelt und hergestellt, darunter:

- AMD

- Apple

- Centaur Technology

- Chips & Technologies

- Cyrix

- DMP Electronics

- Harris Semiconductor

- IBM

- Intel

- KME (U80601)

- National Semiconductor

- NEC Corporation

- NexGen

- Rise Technology

- SGS-Thomson

- Siemens

- SiS

- Texas Instruments

- Transmeta

- UMC

- VIA Technologies

Siehe auch

- Liste der Mikroprozessoren von AMD

- Liste der Mikroprozessoren von Intel

- Liste der x86er-Koprozessoren

- ALU

- 32-Bit

- 64-Bit

- PowerPC

Weblinks

- Großes INTEL CPU Archiv – Viele Bilder und Infos

- sandpile.org – Umfangreiches Archiv für x86-bezogene Dokumentation

- cpu-collection.de – Umfangreiche Prozessor-Sammlung

- Assembler X86 Befehlslisten/OpCode und Beschreibungen

- i8086.de 8086/88 Assembler Befehlsreferenz

- Der x86-Prozessor wird 30 - wie Intel dank IBM alle Gipfel stürmte