Die (Halbleitertechnik)

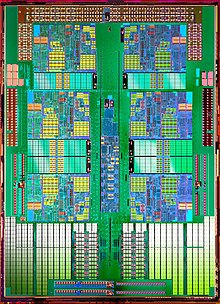

Ein Die ([], englisch für „Würfel“, „Plättchen“, dt. Plural i. A. „Dies“;[1] englischer Plural: dice oder dies [] und die []) ist in der Halbleiter- und Mikrosystemtechnik die Bezeichnung eines einzelnen, ungehäusten Stücks eines Halbleiter-Wafers. Ein solches Die wird üblicherweise durch Sägen oder Brechen des fertig bearbeiteten Wafers in rechteckige Teile (dicing) gewonnen. In der Regel befindet sich auf einem Die ein Bauteil, z. B. ein Transistor, Leuchtdiode, oder eine komplexe Baugruppe, z. B. integrierter Schaltkreis, ein Mikrosystem. Um möglichst lange von der Parallelfertigung auf dem Wafer zu profitieren, findet das Zerteilen im normalen Produktionsprozess zuletzt statt, direkt vor dem Einbau in ein Gehäuse bzw. dem Aufbringen auf einen Schaltungsträger (vgl. Direktmontage). Solche Dies werden dann „Chip“ bzw. „Nacktchip“ genannt.[2] Auch wenn ein Wafer (geplantermaßen) vor der Fertigstellung des Bauteils bzw. der Baugruppe zerteilt wird (sogar noch unstrukturiert ist), werden die Teilstücke als Dies bezeichnet.

Etymologie

[Bearbeiten | Quelltext bearbeiten]

Die Bezeichnung „die“ rührt vom Küchenenglisch her: „slice and dice“ bedeutet – etwa in Bezug auf eine Gurke – wörtlich „erst in Scheiben schneiden und dann würfeln“ bzw. „kleinschneiden“. Dementsprechend beginnt man bei der Herstellung von integrierten Schaltkreisen mit einem – gurkenähnlichen – Siliziumbarren, dieser wird dann „in Scheiben geschnitten“ – daraus entstehen die „wafer“ = „Waffeln“ – und dann „zerhackt“ – daraus entstehen dann die „dice“ = „Würfel“. Da die Wafer sehr dünn sind, sehen die „dice“ allerdings nicht würfelförmig aus, sondern entsprechen in ihrer Form sehr flachen Quadern.

„Bare Chip“

[Bearbeiten | Quelltext bearbeiten]Mit „bare chip“ oder „bare die“ (deutsch „Nacktchip“) werden integrierte elektronische Bauelemente bezeichnet, die nicht herkömmlich in einem Plastik- oder Keramikgehäuse verbaut, sondern ohne Gehäuse weiterverarbeitet werden. Sie werden direkt auf einer Leiterplatte oder einem keramischen Substrat aufgebracht und mittels Drahtbonden elektrisch mit umliegenden Bauelementen verbunden.

Anwendung

[Bearbeiten | Quelltext bearbeiten]

Im Zuge der fortschreitenden Integration werden immer mehr Baugruppen, die zuvor als einzelne Chips nebeneinander auf einer Platine angebracht wurden, auf einem gemeinsamen Chip vereint. Mittlerweile werden auf einem Die mit etwa einem Quadratzentimeter Fläche mehrere hundert Millionen Transistoren für CPUs, GPUs oder RAM untergebracht.

| Produkt | Die-Maße | Die-Fläche (mm²) | Technologieknoten | Transistorzahl (Mio.) | Kommentar/Bauteil |

|---|---|---|---|---|---|

| NE555[3] | 0,000 024 | Timer-IC, erste Version aus 1971 | |||

| Intel 4004[4] | 3 mm × 4 mm | 12 | 10-µm-PMOS | 0,002 3 | Hauptprozessor, erster Mikroprozessor |

| Intel Itanium 2 (Tukwila)[5] | 21,5 mm × 32,5 mm | 698,75 | 65-nm-Bulk-CMOS | 221 | Mehrkern-Hauptprozessor |

| AMD Phenom II X6 | 346 | 45 nm | 750 | Mehrkern-Hauptprozessor | |

| Nvidia Fermi GF110[6] | 520 | 40 nm | 3 000 | Grafikprozessor | |

| AMD Cayman (RV970)[6] | 389 | 40 nm | 2 640 | Grafikprozessor | |

| Intel Core i7-980X | 248 | 32 nm | 1 170 | Mehrkern-Hauptprozessor | |

| AMD FX | 315 | 32 nm | 1 200 | Mehrkern-Hauptprozessor | |

| Nvidia Kepler GK110 B | 533 | 28 nm | 7 100 | Grafikprozessor | |

| AMD Tahiti (R1000)[6] | 365 | 28 nm | 4 310 | Grafikprozessor | |

| Nvidia Pascal GP100[7] | 610 | 16-nm-FinFET | 15 300 | Grafikprozessor | |

| NVIDIA Volta GV100-Chip[8] | 815 | 12-nm-FinFET | 21 100 | Grafikprozessor |

Digitale und analoge Signalschaltungen können immer öfter mit leistungselektronischen Elementen auf einem Chip untergebracht werden (z. B. BiCMOS-Technologie).

Eine Kombination von zwei sich ergänzenden Baugruppen, wie etwa CPU und Cache, auf demselben Chip lässt sich mit dem Begriff „on-Die“ umschreiben: Die CPU hat den Cache „on-Die“, was höhere Taktraten und Busbreiten ermöglicht und damit den Datenaustausch deutlich beschleunigt.

Verarbeitung

[Bearbeiten | Quelltext bearbeiten]Mit der Weiterverarbeitung der Dies – Gehäusung und Integration in die schaltungstechnische Umgebung – beschäftigt sich die Aufbau- und Verbindungstechnik (AVT, engl. packaging).

Als Known Good Die (KGD) bezeichnet man ein entsprechend den Vorgaben getestetes und als gut befundenes Halbleiterplättchen, das je nach Produkt ein einzelnes Bauelement, zum Beispiel einen Transistor, oder auch eine komplexe Schaltung wie einen Mikroprozessor enthalten kann. Gute bzw. defekte Dies können hierzu noch im Wafer-Verbund durch elektrische Nadeltester ermittelt werden. Defekte Bauteile wurden früher durch einen Farbpunkt gekennzeichnet (geinkt) und werden vom nachfolgenden Prozess des Kontaktierens und Einhausens (Zyklus II, engl. Packaging) ausgeschlossen.

Das Verhältnis von brauchbaren zur Gesamtzahl aller auf einem Wafer vorhandenen Dies wird als Ausbeute (engl. yield) bezeichnet und ist eine wichtige Kennzahl zur Beurteilung des Fertigungsprozesses und der Wirtschaftlichkeit einer Produktionslinie.

Literatur

[Bearbeiten | Quelltext bearbeiten]- Graham Neil: Time is right for bare die. In: European Semiconductor, 27, Nr. 11, 2005, S. 11–12.

Weblinks

[Bearbeiten | Quelltext bearbeiten]Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Laut Google: "Halbleiterdice" - 6 Treffer; "Halbleiterdies" - 339 Treffer; Stand: 03/2018

- ↑ Yvonne Attiyate, Raymond Shah: Wörterbuch der Mikroelektronik und Mikrorechnertechnik mit Erläuterungen / Dictionary of Microelectronics and Microcomputer Technology with Definitions. Springer, 2013, ISBN 978-3-662-13444-3, S. 42 (eingeschränkte Vorschau in der Google-Buchsuche).

- ↑ Hans Camenzind: Designing Analog Chips. 2. Auflage. Virtualbookworm.com Publishing, College Station, Texas 2005, ISBN 1-58939-718-5, Kapitel 11: Timers and Oscillators, S. 11-2, 11–3 (englisch, designinganalogchips.com [PDF; 2,5 MB]).

- ↑ Guy De la Bédoyère: The First Computers. Evans Brothers, 2005, ISBN 0-237-52741-3, S. 36 (eingeschränkte Vorschau in der Google-Buchsuche).

- ↑ Lambert Schaelicke, Eric DeLano: Intel Itanium Quad-Core Architecture for the Enterprise. (PDF) 2010, S. 5, abgerufen am 12. Juli 2015 (Präsentationsfolien, Eighth Workshop on Explicitly Parallel Instruction Computing Architectures and Compiler Technology (EPIC-8)).

- ↑ a b c nVidia GK104: 3,54 Milliarden Transistoren auf nur 294mm² Chip-Fläche. 3DCenter.org, 13. März 2012, abgerufen am 21. Juni 2014.

- ↑ Martin Fischer: GTC 2016: Nvidia enthüllt Monster-Chip Pascal mit 16 GByte HBM2 und bis zu 3840 Kernen. In: Heise online. 6. April 2016. Abgerufen am 23. August 2016.

- ↑ Martin Fischer: GTC 2017: Nvidia stellt Riesen-GPU Volta mit 5120 Kernen und 16 GByte HBM2 vor. In: Heise online. 10. Mai 2017. Abgerufen am 15. Oktober 2018.