CRUVI FPGA Card

Die CRUVI FPGA Card ist ein speziell auf die Bedürfnisse von FPGAs ausgerichteter Tochterkartenstandard.

Hintergrund

[Bearbeiten | Quelltext bearbeiten]Diese Erweiterungsbusschnittstelle wurde entwickelt, um ein offenes System von Funktionsmodulen für eine hochleistungsfähige Peripherieverbindung zu schaffen. Der Hauptfokus liegt auf der Unterstützung von FPGA- und FPGA SoC-Geräten aller führenden Hersteller wie Altera, Lattice Semiconductor Corporation, Microchip Technology und Xilinx.

Das Wort CRUVI ist eine Kombination aus dem estnischen Wort „KRUVI“ für Schraube und dem Buchstaben „C“, der sich auf die Hälfte des sechseckigen Schraubenkopfes bezieht. In diesem Fall wurde das „K“ durch ein „C“ ersetzt, um den Bezug zum Schraubenkopf zu betonen. Alle Module werden mit M2-Schrauben mit einem Durchmesser von 2 mm mechanisch fixiert.

CRUVI kann verwendet werden, um benutzerdefinierte Hochleistungsprototypen zu erstellen, für Systemintegration und Tests, um komplexe Systeme aus kleineren Bausteinen schnell zu entwickeln und Kosten zu senken. Es dient als Plattform für Hochleistungs-Halbleiterevaluierungsplatinen und -systeme.

Das Träger Modul liefert die Stromversorgung, die Eingabe/Ausgabe Spannung und steuert die Funktionen der Peripherie Module.

Der CRUVI-Standard existiert sowohl für Geräte mit niedriger Datenübertragungsrate und geringer Pin-Anzahl wie Pmod Schnittstelle, als auch für Hochleistungsgeräte mit hoher Pin-Anzahl HPC, 400 I/O FPGA Mezzanine Card (FMC)-Peripheriegeräte.

Drei Board-to-Board-Steckverbinder sind spezifiziert: CRUVI-LS (Low Speed), CRUVI-HS (High Speed) und CRUVI-GT (Gigabit Transceiver) PCIe Gen 5.0-fähig.

Verschiedene Adapter Module konvertieren Signale von Pmod zu CRUVI-LS (CR00025), von FMC zu CRUVI-HS (CR00101, CR00111) und von FMC zu CRUVI-GT (CR00112).

Geschichte

[Bearbeiten | Quelltext bearbeiten]Internationale Mitwirkende zur Definition der Open Source CRUVI-Spezifikation sind Trenz Electronic GmbH, Arrow Electronics, Samtec, Flinders University, Synaptic Laboratories Ltd, Symbiotic EDA und MicroFPGA UG.

Geschichte der CRUVI Open Source Spezifikation – zur kostenfreien Nutzung unter der Apache-Lizenz 2.0.

| Jahr | Version | Beschreibung | Referenz |

|---|---|---|---|

| 2021 | 1.0.7 -alpha | erste Freigabe | |

| 2024 | 2.0.1 -alpha | neu: CRUVI-GT (Gigabit Transceiver) | [1] |

Aufbau und Beschreibung der Träger Module

[Bearbeiten | Quelltext bearbeiten]Einzelne, doppelte oder dreifache Träger Module sind möglich. Diese haben mehrere Befestigungslöcher.

Ein Trägermodul mit drei Steckplätzen hat die Maaße 67,72 × 57,5 mm². Die Befestigungslöcher (1 bis 6) für M2-Schrauben haben einen Durchmesser von 2,2 mm und benötigen SMD-Abstandshalter zur mechanischen Fixierung. Die PCB-Vorlage CR99201 hat LS- und HS-Anschlüsse mit den Namen: AX, BY und CZ. Die PCB-Vorlage CR99500[2] hat LS-, HS- und GT-Anschlüsse.

- einfach, zweifach und dreifach Träger Module

-

Trägermodul mit Altera MAX 10 FPGA

-

PCB-Vorlage CR99201

-

Trägermodul mit Altera Cyclone V FPGA

-

Maaße der PCB-Vorlage CR99500

-

PCB-Vorlage CR99500

-

Trägermodul Ansicht von oben

Es wird empfohlen, dass alle FPGA-Hostplatinen mit CRUVI-Steckplätzen LiteX-Plattform-Supportdateien bereitstellen.[3]

Aufbau und Beschreibung der Peripherie Module

[Bearbeiten | Quelltext bearbeiten]Es gibt verschiedene Peripheriemodule, die flexibel und skalierbar in Größe und mit LS-, HS- und GT-Anschlüssen möglich sind. Die Befestigungslöcher sind für M2-Schrauben mit einem Durchmesser von 2,2 mm vorgesehen.

Steckverbinder, Pin und Signal Beschreibung

[Bearbeiten | Quelltext bearbeiten]| LS Low Speed | HS High Speed | GT Gigabit Transceiver | |

|---|---|---|---|

| Träger Module Steckverbinder | CLT-106-02-F-D-A-K | SS4-30-3.50-L-D-K | ADF6-20-03.5-L-4-2 |

| 3D STEP Model |  |

|

|

| Peripherie Steckverbinder | TMMH-106-04-F-DV-A-M | ST4-30-1.50-L-D-P | ADM6-20-01.5-L-4-2 |

| 3D STEP Model |  |

|

|

| Pin Anzahl | 12 (6 je Reihe) | 60 (30 je Reihe) | 80 (20 je Reihe) |

| Pin Abstand [mm] | 2 | 0.4 | 0.635 |

| gesteckte Höhe [mm] | 4.78 bis 5.29 | 5 | |

| Geschwindigkeit [GHz] / [Gbps] | 5.5 / 11 | 13.5 / 27 (single ended)

15.5 / 31 (differentielle) |

32 |

| Single ended I/O pins (VCCIO) | 8 | 37 (28 einstellbar) + (9 fix 3.3V) | 8 + I²C |

| max. differential I/O | no | max. 12 LVDS | max. 4 lanes + REFCLK |

| Stromversorgung | einstellbar, 3.3V, 5V | ||

| Stromstärke je Pin [A] | 4.1 (2-Pin) | 1.6 (2-Pin) | 1.34 (4-Pin) |

| max. Temperatur Bereich [°C] | −55 bis 125 | ||

CRUVI-LS Low Speed Pin und Signal Beschreibung

[Bearbeiten | Quelltext bearbeiten]| Pin | Bezeichnung | Signal | Pin | Bezeichnung | Signal |

|---|---|---|---|---|---|

| 1 | SDA | I2C(SDA), SMBUS(SDA) | 7 | D1 | UART(RXD1), SD(D1), SPI(MISO), QSPI(D1), JTAG(TDI) |

| 2 | SCL | I2C(SCL), SMBUS(SCL) | 8 | CLK | UART(RTS), SD(CLK), SPI(CLK), QSPI(CLK), JTAG(TCK) |

| 3 | D3 | UART(RST), SD(TXD0), QSPI(D3), JTAG(nRST) | 9 | D0 | UART(TXD1), SD(D0), SPI(MOSI), QSPI(D0) JTAG(TDO) |

| 4 | SEL | UART(CTS), SD(CMD), SPI(SEL), QSPI(SEL), JTAG(TMS) | 10 | VCC | Power 3.3V |

| 5 | D2 | SMBUS(INT), UART(RXD0), SD(D2), QSPI(D2), JTAG(RFU) | 11 | RFU | noch nicht definiert |

| 6 | GND | Ground | 12 | VBUS | Power 5V |

CRUVI-HS High Speed Pin und Signal Beschreibung

[Bearbeiten | Quelltext bearbeiten]| Pin | Bezeichnung | Notiz | Pin | Bezeichnung | Notiz | Pin | Bezeichnung | Notiz | Pin | Bezeichnung | Notiz |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | RFU1 | 16 | A0_N | LVDS | 31 | GND | Ground | 46 | A5_N | LVDS | |

| 2 | HSIO | 17 | B0_N | LVDS | 32 | A3_P | 47 | B5_N | LVDS | ||

| 3 | ALERT/IRQ | 18 | GND | Ground | 33 | B3_P | LVDS | 48 | GND | Ground | |

| 4 | VCC | 3,3V | 19 | GND | Ground | 34 | A3_N | 49 | GND | Ground | |

| 5 | SDA | 20 | A1_P | LVDS | 35 | B3_N | LVDS | 50 | RFU2_P | ||

| 6 | HSO | 21 | B1_P | LVDS | 36 | VADJ | 1.2 to 3.3V | 51 | DI/TDI | JTAG, SPI(MISO) | |

| 7 | SCL | 22 | A1_N | LVDS | 37 | GND | Ground | 52 | RFU2_N | ||

| 8 | HSRST | 23 | B1_N | LVDS | 38 | A4_P | LVDS | 53 | DO/TDO | JTAG, SPI(MOSI) | |

| 9 | VCC | 3.3V | 24 | GND | Ground | 39 | B4_P | LVDS | 54 | GND | Ground |

| 10 | HSI | 25 | GND | Ground | 40 | A4_N | LVDS | 55 | SEL/TMS | JTAG, SPI(SEL) | |

| 11 | REFCLK | 26 | A2_P | 41 | B4_N | LVDS | 56 | RFU_P | |||

| 12 | GND | Ground | 27 | B2_P | LVDS | 42 | GND | Ground | 57 | MODE | JTAG EN |

| 13 | GND | Ground | 28 | A2_N | 43 | GND | Ground | 58 | RFU_N | ||

| 14 | A0_P | LVDS | 29 | B2_N | LVDS | 44 | A5_P | LVDS | 59 | SCK/TCK | JTAG, SPI(CLK) |

| 15 | B0_P | LVDS | 30 | GND | Ground | 45 | B5_P | LVDS | 60 | VBUS | 5V |

CRUVI-GT Gigabit Transceiver Pin und Signal Beschreibung

[Bearbeiten | Quelltext bearbeiten]| Pin | Bezeichnung | Notiz | Pin | Bezeichnung | Notiz | Pin | Bezeichnung | Notiz | Pin | Bezeichnung | Notiz |

|---|---|---|---|---|---|---|---|---|---|---|---|

| A1 | GND | Ground | B1 | TCK | JTAG | C1 | TDI | JTAG | D1 | GND | Ground |

| A2 | TX3_N | B2 | TMS | JTAG | C2 | TDO | JTAG | D2 | RX3_N | ||

| A3 | TX3_P | B3 | C3 | D3 | RX3_P | ||||||

| A4 | GND | Ground | B4 | C4 | D4 | GND | Ground | ||||

| A5 | TX2_N | B5 | C5 | D5 | RX2_N | ||||||

| A6 | TX2_P | B6 | C6 | D1_N | D6 | RX2_P | |||||

| A7 | GND | Ground | B7 | C7 | D1_P | D7 | GND | Ground | |||

| A8 | B8 | C8 | D8 | CLK0_N | CLK | ||||||

| A9 | B9 | C9 | D9 | CLK0_P | CLK | ||||||

| A10 | B10 | VADJ | 1.2 to 3.3V | C10 | VCC_5V | 5V | D10 | GND | Ground | ||

| A11 | B11 | VCC_3.3V | 3.3V | C11 | VCC_12V | 12V | D11 | GND | Ground | ||

| A12 | B12 | C12 | D12 | GBTCLK0_N | CLK | ||||||

| A13 | B13 | C13 | D13 | GBTCLK0_P | CLK | ||||||

| A14 | GND | Ground | B14 | C14 | D0_N | D14 | GND | Ground | |||

| A15 | TX1_N | B15 | C15 | D0_P | D15 | RX1_N | |||||

| A16 | TX1_P | B16 | S4_LS | AUX IO | C16 | S7_LS | AUX IO | D16 | RX1_P | ||

| A17 | GND | Ground | B17 | S5_LS | AUX IO | C17 | S6_LS | AUX IO | D17 | GND | Ground |

| A18 | TX0_N | B18 | S0_LS | AUX IO | C18 | S3_LS | AUX IO | D18 | RX0_N | ||

| A19 | TX0_P | B19 | S1_LS | AUX IO | C19 | S2_LS | AUX IO | D19 | RX0_P | ||

| A20 | GND | Ground | B20 | SDA_LS | SMBus | C20 | SCL_LS | SMBUs | D20 | GND | Ground |

Vorlagen der Peripherie Module

[Bearbeiten | Quelltext bearbeiten]Es sind verschiedene Einzelperipheriemodule möglich, flexibel und skalierbar durch LS-, HS- und GT-Stecker. Die Befestigungslöcher sind für M2-Schrauben mit 2,2 mm Durchmesser.

Es wird empfohlen, EEPROM mit I2C Schnittstelle zur Identifizierung des Peripheriemodules mit einer bestimmten Adressnummer zu verwenden.

| L x H [mm²] | Geschwindigkeit | PCB Vorlage[2] | Bemerkung |

|---|---|---|---|

| 14 x 14 | LS | CR99001 |

mit Identifikations-EEPROM; Diese Vorlage ist nützlich für I2C, I3C, SPI-Sensor, I2S PDM MEMS Mikrofone, programmierbare Oszillatoren, ADC, DAC oder SPI (QSPI) Flash-Speicher im BGA24- oder SO-8-Gehäuse. |

| 14 x 14 | LS | CR99002 | wie CR99001 mit u.Fl Stecker |

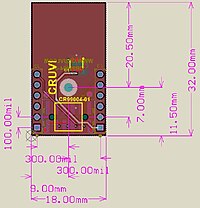

| 22 x 32 | LS | CR99003 |

halbe Länge, mit Identifikations-EEPROM |

| 18 x 32 | LS | CR99004 |

Diese Vorlage eignet sich zur Konvertierung in Pmod Signale (CR00005). |

| 22 x 30 | LS | CR99005 |

halbe Länge, zwei SMA Stecker |

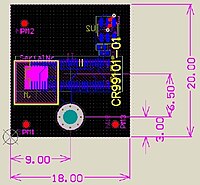

| 18 x 20 | HS | CR99101 |

kleinste Größe HS Modul; Diese Vorlage eignet sich für HyperRAM oder HyperFlash (CR00041), eMMC (CR00049) oder Loopback Adapter für CRUVI-HS (CR00091) |

| 22 x 57.5 | HS | CR99102 |

maximale Größe, einfache Breite HS module; Diese Vorlage eignet sich für Signal Test Adapter zur Untersuchung mit Oszilloskop oder Logikanalysator (CR00026), für Hochgeschwindigkeitsschnittstellen wie USB-C, HDMI (CR00240), MIPI CSI/DSI, SDIO, xGMII Ethernet (CR0020x) und LVDS ADC (1 bis 4 Data Lanes) |

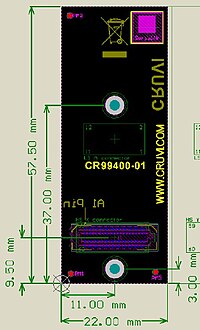

| 22 x 57.5 | GT | CR99400 |

Diese Vorlage eignet sich für HDMI Ausgang (CR00240), JESD204B ADC (CR00401), Loopback Adapter für CRUVI-GT (CR00092) |

Weblinks

[Bearbeiten | Quelltext bearbeiten]- CRUVI Webpage

- Trenz Electronic GmbH entwickelt und produziert CRUVI + FPGA (SoC) Module

- neue FPGA Erweiterungsbusschnittstelle CRUVI erschienen 2023-05-11

- Arrow reveals first Dev Board for Intel Agilex 5 FPGAs, with two more boards planned erschienen 2023-11-27

- Altera Agilex 5 E Series AXE5 Eagle Development Platform mit CRUVI

- Software is integrated into VHDPlus IDE for CRUVI solutions

- Synaptic Laboratories Ltd (SLL) is contributor to the exciting open source CRUVI standard for memory controller

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ CRUVI specification v2.0.1 (2024). Abgerufen am 16. April 2024.

- ↑ a b PCB Vorlage CRUVI Module. 13. März 2024, abgerufen am 5. Mai 2024.

- ↑ LiteX platform support files for FPGA host boards with CRUVI slots. Abgerufen am 2. April 2024.