Benutzer:Steschke/AGC

Der Apollo Guidance Computer (AGC) war der Navigationsrechner des Apollo-Raumschiffs und war das erste Embedded System moderner Ausprägung.

Er entstand als externe Entwicklung durch das Instrumentation Laboratory (heute: Charles Stark Draper Laboratory Inc.) beim Massachusetts Institute of Technology (MIT) im Auftrag der NASA. Hergestellt wurden die Computer für den Einsatz dann von Raytheon. Erstmalig sollte es bei einem Weltraumprojekt möglich sein, dass entscheidende Berechnungen zur Fluglage und Navigation direkt im Raumfahrzeug durchgeführt werden konnten. Grundlegende Entwicklungen waren dafür erforderlich, so beispielsweise die einheitlichen logischen Schaltkreise, die als einfache Widerstands-Transistor-Logik ausgeführt waren. Es musste aber auch ein Weg gefunden werden, wie die Astronauten überhaupt im Weltraum navigieren konnten. Bei den vorhergehenden Mercury- und Gemini-Missionen waren diese Aufgaben überwiegend von der Erde aus wahrgenommen worden. Bei den Flügen zum Mond war das nicht mehr möglich, es wurden wesentlich höhere Anforderungen an die Genauigkeit gestellt, die nur noch mit Messungen im Raumschiff darstellbar waren und wichtige Manöver waren auf der Rückseite des Mondes durchzuführen, also in dessen Funkschatten. Die Lösung war ein Navigationsteleskop und eben der Apollo Guidance Computer.

Baugleiche Computer waren im Kommandoteil (Command Module - CM) und in der Mondlandefähre (Lunar Module - LM) vorhanden. Lediglich die Programme waren unterschiedlich. Dieser glückliche Umstand machte es bei der Apollo-13-Mission möglich, mit dem Computer der Mondlandefähre in engen Grenzen weiterarbeiten zu können.

Auch bei der Apollo-11-Mission gab es bezüglich des Computers eine Besonderheit. Beim Landeanflug gab es einen Speicher- bzw. Instruktionsüberlauf (bei heutigen Computern wäre das wohl einen Absturz wert), dokumentiert als Fehler 1202 und 1201. Verursacht wurde dies durch das versehentlich eingeschaltete Rendezvous-Radar. Dieses Radar diente beim Rückflug vom Mond in die Umlaufbahn der Orientierung zum Apollo-Raumschiff. Beim Landeanflug lieferte es nur eine Flut unnötiger Daten, die die Anflugberechnungen empfindlich störte.

Ausführungen des AGC[Bearbeiten | Quelltext bearbeiten]

Vom AGC wurden zwei verschiedene Varianten gebaut, die erste Version im Block I des Apollo-Raumschiffs und der Block II, bei dem neben Änderungen des Raumschiffs auch der Navigationscomputer dem Stand der Technik angepasst wurde. Der ältere Block I wurde nur für die beiden Apollo-Missionen 1 und 2 konstruiert. Da Apollo 1 nur als Bodentest ausgelegt war und nach dem Unglück die geplante Apollo 2 nie geflogen ist, wurde Block I nie in der bemannten Raumfahrt eingesetzt, sondern nur während der unbemannten Missionen Apollo 4 und 6. Der Block II wurde insgesamt 57 mal gebaut und nicht nur in dem bemannten Apollo-Missionen 7 bis 17 eingesetzt sondern auch in drei Skylab-Missionen, während des Apollo-Sojus-Projekts und dem Fly-by-Wire-Projekt der NASA mit F-8-Flugzeugen.

Die Block-II-Version wurde seit 1966 gebaut, sie übernahm dabei die grundsätzliche Architektur von Block I wurde jedoch mit einem von 1K auf 2K Wort Arbeitsspeicherkapazität verdoppelt und der Festspeicher stieg von 24K auf 36K. Im Zuge des Redesign wurden das Instruction-Set von 11 auf 34 Operationen erhöht und statt der I/O-Register des Block I wurden I/O-Channel implemetiert.

Schaltkreise[Bearbeiten | Quelltext bearbeiten]

Sämtliche logischen Schaltungen im AGC wurden durch nur einen Typ dargestellt, ein NOR-Gatter (nicht-oder) mit drei Eingängen. Die verwendete Widerstands-Transistor-Logik machte es möglich, die Gatter in einfachen integrierten Schaltkreisen zusammen zu fassen. In dieser Technologie lassen sich NOR-Gatter tatsächlich am einfachsten aufbauen. Lediglich ein Widerstand und ein npn-Transistor wird pro Eingang benötigt, für den Ausgang ein weiterer Widerstand. Die Transitoren waren in Emitterschaltung beschaltet, siehe Prinzipschaltbild (links). Die entscheidende Einschränkung dieser Schaltungen war auch beim AGC das geringe Fan-Out von 2 bis 3 beim Block I und von 3 bis 4 beim Block II.

NOR-Gatter (Block I)[Bearbeiten | Quelltext bearbeiten]

In der ersten Ausführung (Block I) war ein Gatter, bestehend aus vier Widerständen und drei npn-Transistoren, in einem TO-5-Gehäuse eingebaut. Abweichend von üblichen Transistoren hatte das Gatter allerdings 5 Anschlüsse, drei Logik-Eingänge, einen Logik-Ausgang und einen Anschluss für die Versorgungsspannung.

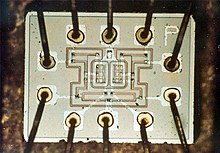

NOR-Gatter (Block II)[Bearbeiten | Quelltext bearbeiten]

Später wurden zwei Gatter auf einem Keramik-Träger (ohne die bis dahin üblichen TO-5-Gehäuse) direkt untergebracht. Dadurch war eine deutlich höhere Packungsdichte möglich. Es war auch nicht mehr erforderlich, die Kontakte zu verlöten, sie wurden in den Block-II-Computern verschweisst. Das führte auch zu einer deutlich höheren Betriebssicherheit, die alten verlöteten Schaltungen hatten immer wieder schlechte Lötstellen. Am unteren Rand des linken Fotos sind die Anschüsse für die Wire-Wrap-Verdrahtung zu sehen.

Speicher[Bearbeiten | Quelltext bearbeiten]

Wie zur Zeit der Apollo-Entwicklung üblich, wurde als Arbeitsspeicher ein Kernspeicher, also einer Matrix aus Ferrit-Ringkernen verwendet. In der Bauform unterschied sich die Ausführung im AGC jedoch von üblichen Kernspeichern dieser Zeit, Der Speicher war in Ketten oder Schnüren (fast könnte man auch Zöpfen sagen) angelegt, um den Speicher in den beengten Gehäusen besser unterbringen zu können. Die NASA und das MIT sprachen daher bei dem Speicher auch von Rope-Memory. Unterschieden wurde dabei auch hier zwischen RAM und ROM (in der Abbildung ist ein ROM dargestellt).

Nur wenige Register wurden als Flipflop aus zwei NOR-Gattern gebildet, wo sie wie die Register heutiger Prozessoren verwendet wurden.

Rope-Memory[Bearbeiten | Quelltext bearbeiten]

Core rope memory ist eine Ausprägung des ROMs für Computer, zuerst genutzt von der NASA in frühen Mars-Sonden und anschließend im AGC, welcher vom MIT entworfen und von Raytheon gebaut wurde.

Entgegen dem üblichen Kernspeicher, welcher zu dieser Zeit als Arbeitsspeicher genutzt wurde, werden die Ferrit-Kerne in einem core rope nur als Transformatoren genutzt. Das Signal von einem Wort-Draht, welches durch einen Kern läuft wird mit dem Bit-Draht verbunden und als binäre "eins" interpretiert, während ein Wort-Draht, welcher den Kern überbrückt nicht mit dem Bit-Draht verbunden wird und als "null" gelesen wird. Im AGC wurden bis zu 64 Drähte durch einen Kern geleitet.

Speicherdichte[Bearbeiten | Quelltext bearbeiten]

Für seine Zeit war die Speicherdichte relativ hoch, in einem core rope memory konnten 72 Kilobytes pro cft, rund 2,5 Megabyte m³, gespeichert werden. Dies entspricht ungefähr dem 18-fachen1 des üblichen Kernspeicher-RAMs.

| Speicher Technologie |

Dateneinheiten pro cft | Dateneinheiten pro m³ | ||

|---|---|---|---|---|

| Bytes | Bits | Bytes | Bits | |

| Core rope ROM | 72K | 576M | ~2.5M | ~20M |

| Magnetic core RAM | 4K | 32K | ~140K | ~ 1M |

DSKY (Display & Keyboard)[Bearbeiten | Quelltext bearbeiten]

Die Eingaben der Astronauten erfolgte über eine einfache 10-er Tastatur mit nur wenigen zusätzlichen Funktionstasten. In modernen Verkehrsflugzeugen findet man heute die Weiterentwicklung, das Flight Management System und dessen Bedienteil, die Control and Display Unit; die Ähnlichkeiten sind eigentlich augenfällig.

Eine DSKY-Einheit befand sich im CM zentral auf der Instrumententafel, eine weitere abgesetzte Einheit direkt am Navigationsteleskop unterhalb des Einstiegstunnels für das LM. Im LM war ein eigener AGC untergebracht, dessen DSKY sich in der Mitte der Frontkonsole befand. Ein abgesetztes Bedienteil war nicht erforderlich, da Teleskop und Sextant unmittelbar darüber an der LM-Decke angebracht waren.

Arbeitsweise[Bearbeiten | Quelltext bearbeiten]

Da mit den oben beschriebenen Schaltungen kaum alle benötigten Rechenoperationen durchgeführt werden konnten, war ein Analogrechner integriert, der z.B. die trigonometrischen Berechnungen durchführte.

zum Analogrechner Anfrage bei NASA r.katz