Mooresches Gesetz

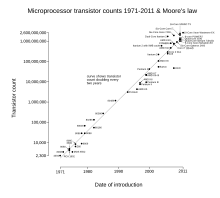

Das mooresche Gesetz (englisch Moore's law; deutsch „Gesetz“ im Sinne von „Gesetzmäßigkeit“) sagt aus, dass sich die Komplexität integrierter Schaltkreise mit minimalen Komponentenkosten regelmäßig verdoppelt; je nach Quelle werden 12 bis 24 Monate als Zeitraum genannt.[1]

Unter Komplexität verstand Gordon Moore, der das Gesetz 1965 formulierte, die Anzahl der Schaltkreiskomponenten auf einem Computerchip. Gelegentlich ist auch von einer Verdoppelung der Integrationsdichte die Rede, also der Anzahl an Transistoren pro Flächeneinheit. Dieser Technologiefortschritt bildet eine wesentliche Grundlage der „digitalen Revolution“.

Ursprünglich sprach Moore selbst von einer jährlichen Verdoppelung, korrigierte 1975 jedoch seine Angabe auf eine Verdoppelung alle zwei Jahre (siehe auch Wirth’sches Gesetz). Moores damaliger Intel-Kollege David House brachte 18 Monate als Abschätzung ins Spiel,[2] was heute die verbreitetste Variante des mooreschen Gesetzes ist und auch den Rahmen bildet, an dem die Halbleiterindustrie ihre Entwicklungspläne auf mehrere Jahre hinaus festmacht. Real verdoppelt sich die Leistung neuer Computerchips im Mittel etwa alle 20 Monate.

Auf Intels Entwicklerforum (IDF) im Herbst 2007 sagte Moore das Ende seines Gesetzes voraus: Es werde wahrscheinlich noch 10 bis 15 Jahre Bestand haben, bis eine fundamentale Grenze erreicht sei. Allerdings prognostizierte Pat Gelsinger, Chef der Digital-Enterprise-Sparte von Intel, bereits ein halbes Jahr später, dass das mooresche Gesetz noch bis 2029 Gültigkeit behalten würde. Im Oktober 2009 erklärte Martin Strobel in seiner Funktion als Pressesprecher von Intel Deutschland im Detail, weshalb man zuversichtlich sei, „das mooresche Gesetz noch eine ganze Weile erfüllen zu können“. [3]

Geschichte

Gordon Moore äußerte seine Beobachtung in einem am 19. April 1965 erschienenen Artikel der Zeitschrift Electronics[4], nur wenige Jahre nach Erfindung der integrierten Schaltung. Die Bezeichnung „mooresches Gesetz“ wurde um 1970 von Carver Mead geprägt. Ursprünglich sagte Moore eine jährliche Verdoppelung voraus, korrigierte diese Aussage jedoch 1975 in einer Rede vor der Society of Photo-Optical Instrumentation Engineers (SPIE) auf eine Verdoppelung alle zwei Jahre. Auslöser dafür war, dass sich die stürmische Entwicklung der Halbleitertechnik der ersten Jahre verlangsamt hatte. In den Medien ist bis heute meist von einer Verdoppelung der Integrationsdichte alle 18 Monate die Rede.

Dieser Wert bezieht sich jedoch auf Angaben aus der Massenproduktion einer zu dem Zeitpunkt aktuellen Technologie-Generation. 2005 lief beispielsweise die konkurrenzfähige Herstellung der Chips für den Weltmarkt mit Strukturen zwischen 130 und 90 nm. In Vorbereitung für die Massenfertigung befand sich die 65-nm-Technik (Gatelänge je nach Technologie ca. 30 bis 50 nm) und im Labor befasste man sich damals bereits mit wiederum kleineren Strukturgrößen. So wurden schon erste Prototyp-Transistoren mit 10 nm Gatelänge gefertigt.[5]

Auslegung

Moores Gesetz ist kein wissenschaftliches Naturgesetz, sondern eine Faustregel, die auf eine empirische Beobachtung zurückgeht. Gleichzeitig kann man von einer „sich selbsterfüllenden Prophezeiung“[6] sprechen, da verschiedenste Industriezweige an der Entwicklung besserer Mikrochips beteiligt sind. Sie müssen sich auf gemeinsame Meilensteine einigen (z. B. optische Industrie mit verbesserten lithographischen Methoden), um wirtschaftlich arbeiten zu können. Die Formulierung des mooreschen Gesetzes hat sich im Laufe der Zeit stark verändert. Sprach Moore noch von der Komponentenanzahl auf einem integrierten Schaltkreis, so ist heute von der Transistoranzahl auf einem integrierten Schaltkreis die Rede, mitunter sogar von der Transistoranzahl pro Flächeneinheit.

Moore stellte fest, dass die Kosten einer Schaltkreiskomponente verfahrensbedingt mit sinkender und steigender Komponentenanzahl anstiegen. Bei niedriger Komponentenanzahl wurde das verfügbare Material nicht voll ausgenutzt, für höhere Komponentenanzahlen mussten experimentelle Verfahren eingesetzt werden, die sich wirtschaftlich noch nicht lohnten. Er bezog seine Beobachtung daher ausschließlich auf das jeweilige Kostenoptimum, also dasjenige Produktionsverfahren und diejenige Komponentenanzahl pro Schaltkreis, bei denen die Kosten pro Schaltkreiskomponente am geringsten ausfielen. Dadurch ist theoretisch klar vorgegeben, welches Herstellungsverfahren und welcher Computerchip zur Überprüfung des mooreschen Gesetzes in jedem Jahr betrachtet werden müssten.

Die unterschiedlichen Formulierungen verzerren die ursprüngliche Beobachtung Moores teilweise bis zur Unkenntlichkeit. Bereits die variable Auslegung des Verdoppelungszeitraums von 12, 18 oder 24 Monaten verursacht beträchtliche Unterschiede. Da Computerchips stark in der Größe variieren, ist es auch durchaus nicht dasselbe, ob man die Transistoranzahl pro Chip oder pro Flächeneinheit betrachtet. Das Weglassen des Kostenoptimums schließlich führt zu einer vollständigen Entfremdung. Ohne Kostenoptimum kann jedes beliebige Produktionsverfahren und jeder beliebige Schaltkreis zur Bestätigung des mooreschen Gesetzes herangezogen werden; ob es sich um einen handelsüblichen Prozessor, extrem teure Hochtechnologie oder experimentelle Schaltkreise, die noch gar nicht käuflich erwerblich sind, handelt, ist in dieser laxen Auslegung ohne Belang. Durch die unterschiedlichen kursierenden Versionen hat das mooresche Gesetz viel von seiner objektiven Aussagekraft eingebüßt.

Schreibweise

Die Komplexität K in Abhängigkeit von der Zeit t des mooreschen Gesetzes folgt einer Exponentialfunktion:

Dabei ist die Rate der Zunahme λ der Kehrwert der Verdopplungszeit T2, multipliziert mit der Konstanten :

Dieser Zusammenhang kann auch in der verkürzten Schreibweise:

dargestellt werden.

Für die Verdoppelungszeit T2 sind mehrere Annahmen gebräuchlich. Oftmals wird T2 = 2 a verwendet, λ beträgt in diesem Fall 0,35 pro Jahr.

Rechenleistung

Dass mit der Anzahl der Transistoren auf einem Computerchip auch die Rechenleistung der Computer linear anwächst, kann aus dem mooreschen Gesetz nicht gefolgert werden. Bei modernen Prozessoren werden immer mehr Transistoren für einen integrierten Speicher (Cache) verwendet, der zur Rechenleistung nur passiv beiträgt, indem er Zugriffe auf häufig benötigte Daten beschleunigt. Als Beispiel sei hier der Vergleich zweier Prozessoren aus der Reihe des Pentium III gegeben. Dabei handelt es sich zum einen um ein „Katmai“ mit einer Taktfrequenz von 500 MHz und externem L2-Cache zum anderen einen „Coppermine“ in der 1-GHz-Variante mit integriertem L2-Cache. Dabei hat sich beim 1-GHz-Coppermine gegenüber dem 500-MHz-Katmai die Taktfrequenz verdoppelt und die Transistoranzahl sogar verdreifacht, dennoch zeigt sich bei diesen vergleichsweise ähnlichen Prozessoren eine Leistungssteigerung um den Faktor 2,2 bis 2,3.

| Prozessor | Transistoren | SPEC-Werte | |

|---|---|---|---|

| Ganzzahl | Gleitkomma | ||

| Pentium III 500 MHz (externer L2-Cache) | 9,5 Mio. | 20,6 | 14,7 |

| Pentium III 1000 MHz (interner L2-Cache) | 28,5 Mio. | 46,8 | 32,2 |

In Mehrkernprozessoren werden mehrere Prozessorkerne auf einem Chip zusammengeführt, die parallel arbeiten und dadurch mehr Leistung erbringen. Hier wird die Verdoppelung der Transistoranzahl hauptsächlich durch die Verdoppelung der Anzahl der Prozessorkerne erreicht. Auch hier tritt jedoch keine Verdoppelung der Rechenleistung ein, denn beim Parallelbetrieb der Prozessorkerne fällt zusätzlicher Koordinierungsaufwand an, der die Leistung wieder schmälert. Zudem sind nicht alle Programmteile im Betriebssystem und bei Anwendungen parallelisierbar, so dass es schwierig ist, alle Kerne gleichzeitig voll auszulasten. Eine einführende Übersicht zu diesem Thema bietet das amdahlsche Gesetz.

Technische Grenzen

Neben Kritik an der fehlerhaften Auslegung des Gesetzes selbst gab es immer wieder Stimmen, die das Ende der Wirksamkeit der mooreschen Faustregel aufgrund unüberwindbarer technischer Hürden voraussagten. Bislang wurden jedoch alle prognostizierten Hürden überwunden, bevor sie einen Knick der mooreschen Exponentialkurve verursachen konnten. Entwicklungspläne, die die Einhaltung des mooreschen Gesetzes sicherstellen sollen, reichen bis ins Jahr 2020 (laut SEMATech).

Zum Vergleich: Transistoren aus der Halbleiterfertigung mit 90 nm haben eine Gatelänge von ca. 50 nm und sind etwa so groß wie ein Influenzavirus. Bei der Herstellung werden solch kleine Strukturen mithilfe fotolithographischer Verfahren hergestellt. Für eine „optische“ Fotolithografie für kleinere Strukturen wurde Mitte der 2000er Jahre die sogenannte Immersionslithografie in der industriellen Produktion eingeführt. Durch dieses Immersionsverfahren konnten die nötigen Auflösungen für die 65-nm-Fertigung und kleiner sichergestellt werden. Für aktuelle (2010) Produkte (45-nm-Knoten bis 28-nm-Knoten) wird die Immersionslithografie mit weiteren Techniken kombiniert, wie dem Double-Exposure- bzw. Double-Patterning-Verfahren, die eine weitere Steigerung der Auflösung auf Grundlage bestehender Techniken ermöglicht. Für noch kleinere Strukturen bei der 16-nm-Technologie und danach wird (wahrscheinlich) ein komplett neues Belichtungsverfahren nötig: EUV. Diese gegenwärtig noch nicht technisch hinreichend umsetzbare EUV-Technik arbeitet mit einer Wellenlänge von 13 nm. EUV ist die gängige Abkürzung für „extremes Ultraviolett“, auch „weiche“ Röntgenstrahlung genannt. EUV kann Glas nicht durchdringen, kann also nicht mit Linsen fokussiert werden, sondern nur über Hohlspiegel reflektiert werden. Ein Hohlspiegel, mit dem das möglich ist, wurde jüngst bei Carl Zeiss SMT entwickelt. Die Spiegeloberfläche muss extremen Anforderungen entsprechen. Es gilt Abweichungswerte kleiner als 0,15 nm zu erreichen. Damit handelt es sich um den derzeit „weltweit ‚präzisesten‘ Spiegel“. [7]

Obwohl der Fortschritt für die nächsten Jahre gesichert scheint, mehren sich Stimmen, die eine Verlangsamung der Zunahme der Integrationsdichte erwarten. Zum einen werde eine technische Grenze erreicht, wenn ein Transistor die Ausdehnung weniger Atome erreiche (siehe auch Tunnelstrom). Zum anderen wachse der finanzielle Aufwand für Entwicklung und Herstellung integrierter Schaltungen schneller als die Integrationsdichte, so dass es einen Punkt geben werde, an dem die Investitionen sich nicht mehr lohnen würden. Bei Annahme eines exponentiellen Wachstums der Entwicklungskosten wäre gleichermaßen eine Grenze durch das verfügbare Kapital vorgegeben. Umgehen ließe sich diese sich anbahnende Grenze durch grundsätzlich neue Technologien. Kandidaten dafür sind die Erforschung von Nanomaterialien wie Graphen, dreidimensionale integrierte Schaltkreise (und somit die Erhöhung der Transistorzahl pro Volumen und nicht mehr nur pro Fläche), Spintronik sowie optische und Quantencomputer. Bei all diesen Technologien würde die Rechenleistung oder Speicherdichte gesteigert, ohne im herkömmlichen Sinn die Dichte an Transistoren zu steigern, sodass das mooresche Gesetz zwar formell an Gültigkeit verlöre, nicht aber zwingend von seinen Auswirkungen her.

Im Bereich höchster Rechneranforderungen (speziell: numerische Strömungssimulation) ist dagegen seit etwa 2003 eine deutliche Verletzung des mooreschen Gesetzes zu beobachten. Auf Basis eines Benchmarks einer kommerziellen Strömungssimulationssoftware durchgeführt im Zeitraum von 1996 bis 2009 zeigt sich deutlich, dass die Zeit die je finitem Volumen (cell) und je Iteration des Solvers benötigt wird, etwa ab 2003 gar nicht oder nur noch marginal sinkt (ca. 10 % nach 2 Jahren statt der dem mooreschen Gesetz entsprechenden 50 %, z. T. weniger bis 0 %). Die Prozessorhersteller haben darauf mit Mehrkern-CPUs reagiert. Allerdings skaliert die meiste Software nicht proportional mit der Zahl der Kerne, d. h., mit zwei Kernen ist die Ausführungszeit mehr als halb so lang wie mit einem Kern. Im schlechtesten Fall ist die Software überhaupt nicht auf Mehrkern-Rechner ausgelegt und die Beschleunigung ist Null. Allerdings läuft auf heutigen PCs viele Software, z. B. Betriebssystem, Virenscanner und Anwendungssoftware parallel, so dass sich auch hier eine Beschleunigung ergibt. Anders verhält es sich im Bereich der Strömungssimulation. Hier sind die meisten Softwarewerkzeuge parallelisiert und skalieren bei angemessen schneller Netzwerktechnik zwischen den Kernen recht linear, das heißt, x-mal mehr Kerne bedeutet auch x-mal so schnell. Damit sind dem Speedup bei der Anwendung nur durch die Latenzzeiten im Netzwerk zwischen den Kernen Grenzen gesetzt.

Siehe auch

Literatur

- S. Hamilton: Taking Moore's law into the next century. In: Computer. Band 32, Nr. 1, 1999, S. 43–48, doi:10.1109/2.738303.

- The Technical Impact of Moore's Law. In: M. Y. Lanzerotti (Hrsg.): IEEE solid-state circuits society newsletter. Band 20, Nr. 3. IEEE, 2006 (PDF).

- R. R. Schaller: Moore's law: past, present and future. In: Spectrum, IEEE. Band 34, Nr. 6, 1997, S. 52–59, doi:10.1109/6.591665.

Weblinks

- Material von Intel

- Moore's Law – Made real by Intel innovation. Auf: Intel.com.

- Moore’s Law 40th Anniversary. Auf: Intel.com. (umfangreiche Presseinformationen)

- Vierzig Jahre Mooresches Gesetz. Auf: Intel.com.

- Computer History Museum: [8]. Auf: computerhistory.org.

- Beat Döbeli Honegger: Moore’s law. In:Beats Biblionetz: Begriffe. (Beat Doebelis Begriffsnetz-Grafik und Definitions-Versionen)

- Christoph Drösser: Die Wie-schnell-wird-aus-Technik-Schrott-Form. Auf:Zeit Online. 14. April 2005

- Ray Kurzweil: The Law of Accelerating Returns. Auf: KurzweilAI.net. 7. März 2001 (Artikel in dem Kurzweil ausgehend vom Mooreschen Gesetz die Beschleunigung der technologischen Entwicklung prognostiziert).

- Meldungen auf Heise online:

- Christof Windeck: Intel und Qinetiq wollen mit III-V-Halbleitern das Mooresche Gesetz fortführen. Auf: Heise-Online. 8. Dezember 2005.

- Jürgen Kuri: Vor 40 Jahren: Electronics druckt Moores Gesetz. Auf: Heise-Online. 19. April 2005 (Artikel über die Hintergründe und Umstände der Veröffentlichung).

Einzelnachweise

- ↑ R. Hagelauer, A. Bode, H. Hellwagner, W. Proebster, D. Schwarzstein, J. Volkert, B. Plattner, P. Schulthess: Informatik-Handbuch. 2. Auflage. Pomberger, München 1999, ISBN 3-446-19601-3, S. 298–299.

- ↑ Moore's Law to roll on for another decade - CNET News

- ↑ Wir sind zuversichtlich, das Mooresche Gesetz noch eine ganze Weile erfüllen zu können. Abgerufen am 20. Juni 2011.

- ↑ G. E. Moore: Cramming more components onto integrated circuits. In: Electronics. Band 38, Nr. 8, 1965, S. 114–117 (PDF).

- ↑ R. Chau, B. Doyle, M. Doczy, S. Datta, S. Hareland, B. Jin, J. Kavalieros, M. Metz: Silicon nano-transistors and breaking the 10 nm physical gate length barrier. In: Device Research Conference, 2003. 2003, S. 123–126.

- ↑ Gordon Moore bezeichnet sein Gesetz als eine „self fulfilling prophecy“, siehe Gordon Moore Says Aloha to Moore’s Law. Auf: the Inquirer. 13. April 2005, abgerufen am 4. März 2009

- ↑ Alexander Stirn: Glatte Spiegel für kleine Chips. www.sueddeutsche.de, 5. Dezember 2007, abgerufen am 19. Juni 2010.

- ↑ Computer History Museum - The Silicon Engine | 1965 - "Moore's Law" Predicts the Future of Integrated Circuits