Leiterplatte

Eine Leiterplatte (Leiterkarte, Platine oder gedruckte Schaltung; englisch printed circuit board, PCB) ist ein Träger für elektronische Bauteile. Sie dient der mechanischen Befestigung und elektrischen Verbindung. Nahezu jedes elektronische Gerät enthält eine oder mehrere Leiterplatten.

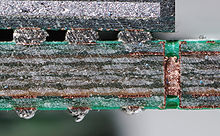

Leiterplatten bestehen aus elektrisch isolierendem Material mit darauf haftenden, leitenden Verbindungen (Leiterbahnen). Als isolierendes Material ist faserverstärkter Kunststoff üblich, bei günstigeren Geräten auch Hartpapier. Die Leiterbahnen werden zumeist aus einer dünnen Schicht Kupfer geätzt, üblich sind 35 µm. Die Bauelemente werden auf Lötflächen (Pads) oder in Lötaugen gelötet. So werden sie an diesen footprints gleichzeitig mechanisch gehalten und elektrisch verbunden. Größere Komponenten können auch mit Kabelbindern, Klebstoff oder Verschraubungen auf der Leiterplatte befestigt werden.

Leiterplattenarten

[Bearbeiten | Quelltext bearbeiten]

Die Leiterplattenarten reichen von einseitigen Leiterplatten über Multilayer bis hin zu Sondertechniken.

- Standardleiterplatten

- Einseitige und zweiseitige Leiterplatten

- Multilayer mit mehreren Lagen (unterschiedlich, je nach Hersteller)

- Sondertechniken (Sondertechniken kommen in allen Industriezweigen zum Einsatz und besitzen besondere Eigenschaften und Anforderungen)

- Flexlam

- Hochstrom: Um den Transport von hohen Strömen und Signalelektronik über eine Leiterplatte zu realisieren.

- Dickkupfer

- Dünnstleiterplatten

- Schleifring: Ein Schleifring wird für die Übertragung und zum Abgreifen von Energie, Signalen und Daten bei sich drehenden Systemen genutzt. Einsatzgebiete sind beispielsweise bei Industrierobotern und Windkrafträdern. Voraussetzung für die Zuverlässigkeit und Lebensdauer einer Schleifringoberfläche ist die richtige Applikation der Edelmetallbeschichtung.

- HDI-Leiterplatte

- IMS-Leiterplatte

- Leiterplatten auf Glas

Herstellung

[Bearbeiten | Quelltext bearbeiten]

Entwurf

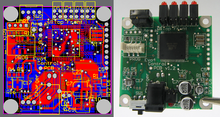

[Bearbeiten | Quelltext bearbeiten]Der Leiterplattenentwurf (Layout) erfolgt heute meist mit einer Software, die neben den Leiterzug-Daten auch den Schaltplan und oft Stücklisten sowie auch Daten wie Lotpasten-Muster oder Bestückungsdruck enthält. Der Leiterplattenentwurf kann von den Leiterplatten-Layout-Programmen in einem Standardformat ausgegeben werden. Die meisten Leiterplattenhersteller verarbeiten die Formate Gerber RS-274X, Excellon oder Sieb & Meyer. Dabei werden die Projektdaten der Leiterplatte aufgeteilt. Der erste Teil besteht aus Gerber-Daten für die Topographie der Leiterplatten. Damit werden z. B. der Leiterbahnverlauf und die Lokalisierung von PADs etc. dokumentiert. Der zweite Teil besteht aus den Bohrdaten im Format der Excellon- oder Sieb & Meyer-Daten.

Die Leiterplattenentflechtung (manuell oder mit einem Autorouter) ist der Hauptinhalt des Entwurfes. Dazu kommen technologische Angaben wie Kupferstärke, Platinen-Fertigungstechnologie und Oberflächenart. Jetzt erfolgt die Übergabe der Daten an den Leiterplattenhersteller.

- CAM

Der Leiterplattenhersteller wird die Daten zuerst in eine CAM-Station einlesen. Dort wird zunächst der Lagenaufbau extrahiert, damit die Funktion der Daten beim System bekannt ist. Dann wird mittels Design Rule Checks geprüft, ob die angelieferten Daten fehlerfrei und fertigbar sind. Dann wird ein Produktionspanel erstellt. Es besteht aus den für die Fertigung benötigten Programmen. Dazu gehören Ausgaben für Filmplotter/Imager, Bohr-, Fräs- und Ritzdaten, AOI (Automatic Optical Inspection) Ausgaben, Elektrische Prüfprogramme, und vieles mehr.

Die Produktionsdaten sind in nach Funktion getrennten Ebenen strukturiert:

- Muster einer oder mehrerer Kupferlagen (Leiterzüge und Flächen)

- Bohrlöcher (Lage, Tiefe und Durchmesser)

- Umriss und Durchbrüche

- Bestückungsplan oben und unten

- Lötstopplack oben und unten

- Bestückungsdruck oben und unten

- Klebepunkte und Lotpastenmuster für SMD-Bauteile oben und unten

- Partielle Metallisierungen (zum Beispiel Vergoldung für Kontaktflächen)

Serienfertigung

[Bearbeiten | Quelltext bearbeiten]Photochemisches Verfahren

[Bearbeiten | Quelltext bearbeiten]

Der größte Teil einseitiger und doppelseitiger durchkontaktierter Leiterplatten wird fotochemisch hergestellt.

Die heutige Reihenfolge der Herstellungsschritte ist:

- Bohren

- Durchkontaktieren (bei doppelseitigen Leiterplatten)

- Fotoresist laminieren

- Belichten

- Entwickeln

- Ätzen

- Spülen

- Trocknen

Danach folgen je nach Bedarf weitere Nachbearbeitungsschritte.

Ursprünglich wurde das Bohren und Durchkontaktieren erst nach dem Ätzen der Leiterplatte vorgenommen. Seitdem aber der Fotolack durch sog. Trockenresist, also eine fotoempfindliche Folie ersetzt wurde, konnte die Reihenfolge der Produktionsschritte verändert werden. Vorteil ist, dass nun nicht mehr vor dem Durchkontaktieren eine Maske auf die Platine aufgebracht werden muss, die das Aufwachsen des Kupfers an unerwünschten Stellen verhindert. Da zu diesem Zeitpunkt noch die gesamte Leiterplatte von Kupfer bedeckt ist, erhöht sich nur die Schichtdicke der Kupferfolie. Die metallisierten Bohrungen werden während des Ätzvorganges von der Fotoresistfolie beidseitig abgeschlossen.

Die Herstellung der Leiterbahnen erfolgt in der Regel fotolithografisch, indem eine dünne Schicht lichtempfindlichen Fotolacks auf die Oberfläche der noch vollständig metallisierten Platte aufgebracht wird. Nach der Belichtung des Fotolacks durch eine Maske mit dem gewünschten Platinenlayout sind je nach verwendetem Fotolack entweder die belichteten oder die unbelichteten Anteile des Lacks löslich in einer passenden Entwicklerlösung und werden entfernt. Bringt man die so behandelte Leiterplatte in eine geeignete Ätzlösung (z. B. in Wasser gelöstes Eisen(III)-chlorid oder Natriumpersulfat oder mit Salzsäure + Wasserstoffperoxid,[1]) so wird nur der freigelegte Teil der metallisierten Oberfläche angegriffen; die vom Fotolack bedeckten Anteile bleiben erhalten, weil der Lack beständig gegen die Ätzlösung ist.

Prototypen können auch durch Fräsen der Kupferschichten strukturiert werden („Isolationsfräsen“, s. u. Bild zu Lötrasterplatinen). Solche Platinen bestehen nicht aus Leiterbahnen, sondern aus Flächen, die voneinander durch Frässpuren getrennt sind.

Die Kupferschichten können nach dem Ätzen galvanisch verstärkt werden.

Die Herstellung der Bohrungen zur Aufnahme bedrahteter Bauteile sowie für Durchkontaktierungen erfordert aufgrund des Glasfaser-Anteils des Trägermaterials Hartmetallwerkzeuge. Wenn Bohrungen an den Innenwänden metallisiert werden, entstehen Durchkontaktierungen. Die Metallisierung der Bohrungen (isolierende Flächen) erfordert eine Bekeimung, nachfolgende stromlose Abscheidung einer dünnen Kupferschicht und schließlich deren elektrolytische Verstärkung.

Zusätzlich können galvanisch auf Teilflächen oder der gesamten Kupferfläche metallische Schutz- und Kontaktschichten aus Zinn, Nickel oder Gold aufgebracht werden. Dünne Vergoldungen erfordern zum Kupfer hin eine Diffusionssperrschicht (Nickel-Sperrschicht).

Danach wird Lötstopplack (grüne Lackschicht der Leiterplatte im Foto) aufgebracht, der die Leiterbahnen abdeckt und nur die Lötstellen frei lässt. Damit lassen sich Lötfehler vermeiden, beim Schwalllöten spart man Zinn und die Leiterbahnen werden vor Korrosion geschützt. Die frei bleibenden Lötstellen (Pads und Lötaugen) können mit einem physikalischen Verfahren (hot air leveling) mit einer Zinnschicht und zusätzlich mit einem Flussmittel überzogen werden, die besseres Löten ermöglicht.

Lotpaste-Inseln zum Auflöten von SMD-Bauteilen werden mittels einer Lotpasten-Maske aufgebracht. Sie ist aus Metallblech und enthält an den Stellen Löcher, wo Lotpaste aufgetragen werden soll. Die Masken werden durch Laserfeinschneiden hergestellt. Ein weiterer möglicher Verfahrensschritt bei der SMD-Bestückung ist das Aufbringen von Kleberpunkten, die die Fixierung der Bauteile beim Bestücken (Pick and place) bis zum Löten sicherstellt.

Oft tragen Leiterplatten einen per Siebdruck hergestellten Bestückungsdruck, der in Verbindung mit dem Schaltplan Montage und Service erleichtert.

Stanztechnik und Drahtlegetechnik

[Bearbeiten | Quelltext bearbeiten]Zwei weitere wichtige Herstellungsverfahren für Leiterplatten sind die Stanztechnik und Drahtlegetechnik. In Stanztechnik werden Leiterplatten für sehr große Stückzahlen hergestellt. Die Technik eignet sich nur für einseitige Leiterplatten aus Pertinax oder unverstärkten Kunststoffen. Dabei wird Basismaterial ohne Kupferauflage verwendet, eine Kupferfolie mit einer Klebstoffschicht wird auf das Basismaterial gelegt und dann mit einem Prägestempel die Leiterbahnformen ausgestanzt und gleichzeitig auf das Basismaterial gedrückt. In einem Arbeitsgang werden dabei die Kontur der Leiterplatte und die Bohrungen gestanzt sowie das Leiterbild ausgestanzt und mit dem Basismaterial verklebt.

Für kleine Serien und für spezielle Anwendungen, die eine hohe Stromfestigkeit der Leiterplatte benötigen, wird die Drahtlegetechnik angewandt. Dabei verlegt eine Maschine isolierte Drähte auf dem Basismaterial, die mittels Ultraschallschweißens sowohl an den Lötpunkten angeschlossen, als auch auf der Oberfläche des Basismaterials befestigt werden.

Mit „Nutzen“ wird bei der Anfertigung von Leiterplatten das Zusammenfassen mehrerer kleinerer Layouts auf einer großen Platine bezeichnet. Der Begriff stammt aus der Drucktechnik. Die gesamte Verarbeitungskette erfolgt soweit möglich mit diesem Nutzen. Durch geschickte Anordnung unterschiedlicher Entwürfe können die üblicherweise rechteckigen Formate des Basismaterials auch bei abweichenden, beispielsweise L-förmigen Geometrien gut ausgenutzt werden. Für die anschließend erforderliche Zerteilung der Platine ist der Begriff Nutzentrennung gebräuchlich.

Siebdruck

[Bearbeiten | Quelltext bearbeiten]Anstelle des fotochemischen Verfahrens kann für die Abdeckung der Leiterzüge vor dem Ätzen auch die Siebdrucktechnik verwendet werden. Diese ist insbesondere für einseitig beschichtetes Material und wenig komplexe Leiterplatten geeignet.

Prototypen

[Bearbeiten | Quelltext bearbeiten]

Vor der Serienfertigung werden meist ein oder mehrere Prototypen erstellt und getestet, um im Fehlerfall die hohen Kosten für die Erstellung der Fotomasken zu vermeiden.

Dazu gibt es folgende Möglichkeiten:

- Fertigung im Pool

- Hersteller bieten die Fertigung von Einzelstücken und Kleinstserien im „Pool“ an, d. h. mehrere Einzelstücke als Nutzen (siehe oben) werden auf einer großen Platte gebohrt, durchkontaktiert, belichtet, geätzt und danach ausgefräst.

- Fräsen

- Bei der Frästechnik werden mit einem Stiftfräser Trennlinien zwischen den Leiterflächen hergestellt. Dabei bleibt alles Kupfer stehen (Inselverfahren). Die nasschemischen und fotolithografischen Schritte entfallen. Viele ECAD-Programme können CNC-Programme generieren, mit denen Prototypen und Kleinserien schnell gefertigt werden können.

- Tonertransfermethode

- Das Layout wird mit einem Laserdrucker spiegelverkehrt auf geeignetes Papier oder eine hitzebeständige Folie gedruckt und anschließend mit Bügeleisen oder Laminiergerät auf die Platine „aufgebügelt“. Der Toner wird dabei wie in der Fixiereinheit des Druckers leicht flüssig und verbindet sich mit dem Kupfer der Platine. Anschließend wird das Papier wieder mit Wasser abgelöst – der Toner verbleibt auf dem Kupfer. Darauf folgt das Ätzen des Kupfers, wobei die vom Toner abgedeckten Stellen stehenbleiben. Der Toner wird anschließend abgelöst. Es können Ungenauigkeiten durch Papiertransport im Drucker sowie durch Dehnen und Schrumpfen des Papiers durch die Erhitzung auftreten. Wird eine transparente Folie bedruckt, kann eine Fotomaske hergestellt werden, um mit Fotolack beschichtetes Basismaterial zu belichten.

-

Leiterplatte mit Schutzschicht nach Tonertransfermethode. Korrekturen mit Filzstift.

-

Leiterplatte nach dem Ätzen; im Hintergrund die vom Kupfer grüne Ätzlösung.

-

Nach der Entfernung der Schutzschicht treten die Leiterbahnen als blankes Kupfer zutage.

- Stifte

- Die Leiterbahnen und Lötaugen werden direkt mit einem wasserfesten Filzstift (sog. Permanent Marker) auf das Basismaterial übertragen. Auf diese Weise kann auch aus einer durchsichtigen Kunststofffolie eine Fotomaske für das Photopositivverfahren hergestellt werden. Die Farbe auf dem Basismaterial schützt während des Ätzens die abgedeckten Flächen. Nach dem Ätzen wird die Farbe mit Spiritus oder Aceton entfernt. Wird zum Zeichnen stattdessen gelöstes und gefärbtes Kolophonium in einer Röhrchenfeder verwendet, kann auf die Entfernung des Abdecklacks verzichtet werden.

- Anreibesymbole

- Manche Hersteller vertreiben Anreibesymbole, die Lötaugen, Leiterbahnteile oder elektrische Symbole darstellen. Diese werden – ähnlich wie Abziehbilder – auf die Leiterplatte aufgelegt und angerieben. Die aufgebrachten Symbole schützen dann das Kupfer unter ihnen während des Ätzvorganges. Dieses Verfahren wird auch in Kombination mit einem Filzstift angewendet (z. B. Lötaugen mit Anreibesymbolen, Leiterbahnen mit Filzstift). Nach dem Ätzen werden die Symbole mit Aceton oder durch Abkratzen entfernt. Lötlack, der oft aufgebracht wird, um die Fließeigenschaften des Lötzinns zu verbessern, löst ebenfalls die Symbole. Auch dieses Verfahren kann zur Massenproduktion auf eine Folie für das Photopositivverfahren angewendet werden.

- Ölmethode

- Bei Bastlern ist die „Ölmethode“ bekannt. Dabei wird das Layout mit höchster Schwärzung mit dem Laserdrucker auf normales Schreibpapier gedruckt und dann mit Öl getränkt, wodurch das Papier weitestgehend transparent wird. Die Belichtung des mit Fotolack beschichteten Basismaterials durch diese Maske hindurch kann mit einer üblichen UV-Quelle oder auch Sonnenlicht erfolgen.

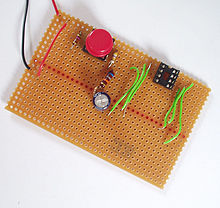

Die Schaltung selbst kann mit Experimentierplatinen getestet werden. : Lochrasterplatinen weisen Bohrungen oder Lötaugen (einseitig oder durchkontaktiert) mit einem Rastermaß auf, das für Elektronikbauteile üblich ist, also 2,54 mm, was 0,1 Zoll (= 100 mil) entspricht, (für die selteneren metrischen Bauteile 2,5 mm) oder die Hälfte davon. Verbindungen können durch Löten mit Schaltdraht, in Fädeltechnik, in Wickeltechnik oder durch einfaches Stecken hergestellt werden. Oft sind mehrere Augen bereits durch Leiterbahnen verbunden (z. B. für Betriebsspannungen) oder es sind längere und kürzere Leiterbahnen bereitgestellt, um praktischen Anforderungen näherzukommen. Auch komplett mit parallelen Leiterbahnen versehene Experimentierplatinen (Lötstreifenplatine) sind üblich. Diese können nach Bedarf mit einem Werkzeug aufgetrennt werden, indem die Leiterbahn durchgeritzt wird. Zudem gibt es kleine Experimentierplatinen, passend für gängige SMD-Gehäuseformen, um deren Anschlüsse auf das Raster zu adaptieren.

Geschichte

[Bearbeiten | Quelltext bearbeiten]

Vor der Einführung von Leiterplatten wurden elektronische Schaltungen frei verdrahtet, ggf. unter zusätzlicher Verwendung von Lötleisten. Mechanische Stützpunkte waren dabei Bauteile wie Potentiometer, Drehkondensatoren, Schalter mit ihren Lötösen sowie die Fassungen von Elektronenröhren. Je nach Hersteller bemühte man sich um übersichtlich rechtwinklige Anordnung der Bauelemente oder wählte immer die direkte, schräge Verbindung. Da die Bauelemente, wie Kondensatoren oder Widerstände, damals noch recht groß und lang waren, konnten sie Distanzen von einigen Zentimetern überbrücken.

Geräte dieser Art waren nur von Hand und mit Kenntnis des Verdrahtungsplanes zu fertigen.

Leiterplatten-Vorläufer ab den 1920er Jahren waren gestanzte Leiterzüge, die auf Hartpapier aufgenietet wurden. Bauelemente (Widerstände, Kondensatoren) wurden ohne Lötverbindung zwischen Blechfedern getragen. Paul Eisler, ein Wiener Elektronik-Ingenieur, ließ sich 1943 das Prinzip der gedruckten Leiterplatte patentieren[2], das aber lange Zeit neben der regulären Handverdrahtung ein eher unbedeutendes Schattendasein fristete. Erst mit der zunehmenden Miniaturisierung der Elektronik nahm die Bedeutung dieser Technik zu.

In der Anfangszeit um 1940 wurden Schaltkreise auch durch Siebdrucken von Silberleitlack auf der Grundplatte hergestellt. Auf Keramiksubstrate gedruckte und eingebrannte Leiterbahnen und Widerstände werden demgegenüber unter dem Begriff Dickschichttechnik geführt.

Fertigungstechnik

[Bearbeiten | Quelltext bearbeiten]Der Einsatz von Leiterplatten begann Anfang der 1950er Jahre durch die von Fritz Stahl gegründeten Ruwel-Werke in Geldern am Niederrhein.

Bei gedruckten Schaltungen werden die Anschlussdrähte der Bauteile von oben durch Bohrlöcher durch die Leiterplatte gesteckt (engl. Through Hole Technology, THT) – eine auch heute noch weit verbreitete Technik. Auf der Unterseite (Löt-, Leiter- oder L-Seite) befinden sich die Kupferleiterbahnen, an denen sie festgelötet werden. Das erlaubt eine vereinfachte und automatisierbare Fertigung, gleichzeitig sinkt die Fehlerrate bei der Produktion, da Verdrahtungsfehler damit für die Schaltung auf der Leiterplatte ausgeschlossen werden.

Komplexere einlagige Leiterplatten erfordern zusätzliche Verbindungen, die nicht im Layout herstellbar sind. Diese werden durch Lötbrücken mittels abgewinkelter Drähte oder Null-Ohm-Widerstände hergestellt. Letztere lassen sich besser in Bestückungsautomaten einsetzen. Alternativ nutzt man für diese Verbindungen Kupferbahnen auf beiden Seiten der Leiterplatte (doppellagige Leiterplatte, DL). Verbindungen zwischen oberer (Bestückungs- oder B-Seite) und unterer Seite wurden durch Löten eingepresster Stifte oder Niete erzeugt.

Erst in den 1960er Jahren wurden diese Verbindungen (Durchkontaktierungen, DK, engl. vias) durch die Leiterplatte hindurch chemisch durch Metallisierung der Lochwände der Bohrungen erzeugt.

Aus Kostengründen werden auch heute noch einlagige Leiterplatten hergestellt, wenn die Schaltung es erlaubt. Gegenüber einer doppelseitigen, durchkontaktierten Leiterplatte liegen die Kosten für eine gleich große einseitige Leiterplatte bei 25–50 %.

Ein erheblicher Teil der weltweit hergestellten Leiterplatten wird auch heute noch von Hand bestückt, obwohl es bereits seit ca. Mitte der 1970er Jahre Bestückungsautomaten gibt. Moderne Leiterplatten mit hoher Packungsdichte und oberflächenmontierbaren Bauteilen (SMD) können allerdings nur teilweise von Hand bestückt werden. Sogenannte „Pick & place“-Automaten übernehmen die Handhabung der manchmal weniger als 1 mm² großen Bauteile. Zunehmend werden im Anschluss an das Reflowlöten der auf beiden Seiten bestückten SMD die THT-Bauelemente von Hand bestückt und anschließend selektiv gelötet. Bis auf QFN, BGA sowie sehr kleine 0201 milli-Zoll-Bauteile können nahezu alle SMD-Bauteile problemlos von Hand gelötet werden. Problematisch von Hand zu löten sind Leistungsbauelemente (unabhängig von der Bauform) mit einem großen Pad an der Unterseite zur Wärmeabfuhr. Diese Leistungsbauelemente sowie QFN- und BGA-Bauteile können unter Umständen trotzdem noch von Hand zu gelötet werden, beispielsweise mit einer Heißluftpistole. Allerdings kann das Bauteil oder Bauteile in der Umgebung dabei Schaden nehmen, falls es zu lange erhitzt wird.

Layout

[Bearbeiten | Quelltext bearbeiten]

In den 1960er Jahren zeichnete man das Layout (Leiterbahnen-Struktur) im Maßstab 2:1 mit Tusche oder in Klebetechnik mit Layoutsymbolen und Kleberollen (Brady) auf Rasterfolien. Später erstellte man an Programmierarbeitsplätzen NC-Programme zur Steuerung eines Lichtzeichengerätes, welches den zur Fotolithografie erforderlichen Film herstellte. Danach verwendete man Computer, um die Zeichnungen der verschiedenen Kupfer- und Drucklagen sowie das NC-Steuerprogramm für die Herstellungen der Bohrungen zu erzeugen.

Aktuelle Layoutprogramme für die sog. Electronic Design Automation (EDA) ermöglichen die Erzeugung eines Verbindungsplanes und der entsprechenden Darstellung („Rattennest“) aus einem Stromlaufplan und beinhalten umfangreiche Bauteil-Bibliotheken, in denen für jedes Bauteil auch die Gehäusegeometrien, technische Daten und die Lage und Größe der Lötpads (englisch Footprint, für „Fußabdruck“) enthalten sind. Der Footprint bezeichnet die Abmessungen der Lötaugen bei der Through Hole Technology (THT) bzw. die Abmessungen der Lötpads bei Surface Mounted Devices (SMD) für ein bestimmtes Bauteil auf der Leiterplatte.

Die automatische Leiterplattenentflechtung anhand eines gegebenen Stromlaufplanes und Design-Regeln der elektrischen Verbindungen ist heute bei einfachen Leiterplatten möglich (Autoplacement und Autorouting). An seine Grenzen stößt dieses Verfahren bei komplexen Leiterplatten, die viel Erfahrung bei der Entflechtung erfordern (z. B. bei Mobiltelefonen). Auch eine Steigerung der Computer-Rechenleistung bringt keine Verbesserung, da die Eingabe der komplexen Design-Vorgaben teilweise mehr Zeit in Anspruch nimmt als die manuelle Entflechtung.

Die Strombelastbarkeit (Stromdichte) von Leiterbahnen ist ein wichtiger Design-Aspekt. Sie kann wesentlich höher als diejenige von Massivdrähten liegen, da das Substrat durch Wärmeleitung kühlt.[3] Layout-Software kann die Strombelastbarkeit berücksichtigen.

Weitere Aspekte sind:

- Bei hohen Frequenzen und Impuls-Steilheiten ist die Wellenimpedanz der Leiterbahnen von Bedeutung (siehe Streifenleitung).

- Bei Digitalschaltungen mit hoher Taktfrequenz muss darauf geachtet werden, dass zusammengehörende Leiterbahnen (Bus) dieselbe Länge haben, so dass die Signale am Ende der Leiterbahnen gleichzeitig ankommen.

- Bei analogen Signalen (besonders Audioanwendungen mit hohem Dynamikumfang) müssen Masseschleifen (auch Erdschleifen, Brummschleifen genannt) vermieden werden.

- Bei hohen elektrischen Spannungen oder hohen Impedanzen müssen wegen der Kriechstromfestigkeit zwischen den Leiterbahnen bestimmte Mindestabstände (Aura) eingehalten werden. Optokoppler, die Netz- und Signalstromkreise galvanisch trennen verbinden, haben die Pins des DIP-Gehäuses gespreizt oder in die Leiterplatte ist unter dem Bauteil ein Schlitz gefräst.

EMV-gerechtes Layout

[Bearbeiten | Quelltext bearbeiten]Die kapazitive und induktive Verkopplung der Leiterbahnen, deren Empfänglichkeit gegenüber externen elektromagnetischen Feldern sowie die Abstrahlcharakteristik (Störemission) wird unter dem Sammelbegriff Elektromagnetische Verträglichkeit (EMV) beschrieben. Entwurfs-Software kann ansatzweise auch EMV-Aspekte innerhalb der Platine berücksichtigen.

EMV-gerechtes Leiterplattenlayout ist durch Vorschriften zur Störabstrahlung oder die Funktion des Gerätes motiviert. Regeln sind beispielsweise möglichst kurze Leiterbahnen, sodass sie nicht als Antenne wirken, sowie die möglichst parallele Rückführung der Ströme hochfrequenter und leistungsintensiver Signale bzw. deren Betriebsspannung.[4]Hauptplatinen wie das mit vier Kupferlagen produzierte K7S5A aus dem Jahr 2001, sowie der teilweise mit 4 Kupferlagen (Layern) aufgebaute Lerncomputer Gigatron TTL haben zum Beispiel je ein Layer als Masse sowie als Betriebsspannung. Diese Layer sind daher induktionsarm und besonders störende oder störempfindliche Leitungen können zwischen sie eingeschlossen werden.

Schaltnetzteile weisen besonders hohe Störpegel auf und erfordern kurze breite Leiterzüge für deren typische stromstarke Rechteckimpulse.

Längere Signalleitungen können aufeinander kapazitiv oder induktiv koppeln. Dementsprechend können sie mit Masseflächen umgeben werden, es muss genügender Abstand vorliegen oder die Kopplung muss kompensiert werden.

In den 1990er Jahren gab es in Leiterplatten-CAD-Programmen noch keine Möglichkeit, das EMV-Verhalten von Leitungen und Anschlüssen zu definieren. Es war Erfahrung notwendig. Inzwischen ist es zwar möglich, Leitungsimpedanzen, Laufzeiten, Koppelung und Abstrahlung mathematisch zu simulieren, Erfahrung und das Wissen um die physikalischen Zusammenhänge sind jedoch weiterhin erforderlich, um die steigenden EMV-Anforderungen umzusetzen.

Leiterplattentechnologien

[Bearbeiten | Quelltext bearbeiten]

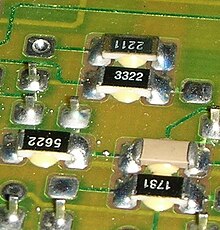

Ein großer Teil der Leiterplatten in elektronischen Geräten wird auch heute noch aus einseitig kaschiertem Material und mit bedrahteten Bauteilen hergestellt (Durchsteckmontage, kurz THT von engl. through hole technology). Mit fortschreitender Miniaturisierung werden auf deren Unterseite zunehmend SMD-Bauteile (von engl. Surface Mounted Device) eingesetzt, während die Durchsteckbauelemente von oben bestückt werden. Die SMD-Bauteile können zusätzlich geklebt sein, sodass sie beim Löten nicht abfallen.

Die teureren durchkontaktierten Platinen sowie noch teurere Mehrlagenplatinen werden bei komplexeren (z. B. Computer), zuverlässigeren (z. B. Industrieelektronik) oder miniaturisierten (z. B. Mobiltelefone) Baugruppen eingesetzt.

SMD-Leiterplatten

[Bearbeiten | Quelltext bearbeiten]

Mitte der 1980er Jahre begann man damit, unbedrahtete Bauteile zu fertigen, die direkt auf die Leiterbahnen zu löten waren (SMD). Diese ermöglichten es, die Packungsdichte zu erhöhen und trugen zu einer enormen Verkleinerung von elektronischen Geräten bei. Zudem ist es möglich, SMD auf beiden Seiten einer Leiterplatte zu platzieren.

Zum Bestücken werden bei gemischt bestückten Platinen (THT und SMD) zunächst die auf der Unterseite (Sekundärseite) anzubringenden SMD auf die Platine geklebt, danach der Kleber ausgehärtet und die Leiterplatte umgedreht, um die andere Seite mit SMD und ggf. THT-Bauteilen zu bestücken. Das Löten der Unterseite kann nun mittels Wellenlöten (Schwallöten) geschehen, sofern die auf der Unterseite angebrachten Teile geeignet sind, durch die Lotwelle zu laufen.

Das Reflow-Löten erfordert das vorherige Aufbringen von Lotpaste (per Hand, per Automat, mittels Maske oder im Direktdruck/Dispenser.[5]) Danach werden die Bauteile platziert. Oft reicht die Adhäsion des geschmolzenen Lotes aus, um die SMDs auch ohne Kleber zu halten. Bei gemischt bestückten Platinen (SMD und THT) müssen die THT-Bauteile mit selektivem Wellenlöten (bewegte Lötdüsen, aus denen flüssiges Lot austritt) oder per Hand gelötet werden, wenn die Unterseite nicht durch den Schwall laufen kann (z. B. unverklebte SMD, Kantensteckverbinder, ungeeignete Abstände und Orientierungen). Andererseits gibt es viele Bauteile (z. B. Polypropylen-Folienkondensatoren, Transformatoren), die nicht durch den reflow-Ofen laufen können und daher nachbestückt werden müssen.

Ein wesentlicher Vorteil von SMD-Bauteilen ist die Handhabbarkeit in Bestückungsautomaten. Bei bedrahteten Bauteilen ist es immer ein wesentliches Problem, mit allen Anschlüssen die Bohrungen zu treffen und die zulässigen Biegeradien der Anschlussdrähte mit einem Biegemaß einzuhalten, weshalb große bedrahtete Bauteile auch heute noch in ansonsten automatisierten Fertigungen von Hand eingesetzt werden.

Mehrlagige Leiterplatten

[Bearbeiten | Quelltext bearbeiten]

Um die höchstmögliche Packungsdichte bei SMD auszuschöpfen, werden doppelseitige Leiterplatten verwendet und beidseitig bestückt. Später begann man, Mehrlagen-Leiterplatten zu verwenden, indem man mehrere dünnere Leiterplatten mit sog. Prepregs aufeinanderklebte. Diese Multilayer-Leiterplatten[6] können bis zu etwa 48 Schichten haben. Üblich sind jedoch vier bis acht Lagen in Computern und bis zu zwölf Lagen in Mobiltelefonen. Die Verbindungen zwischen den Lagen werden mit Durchkontaktierungen („Vias“) hergestellt.

In vielen Fällen ist die Verwendung von Multilayer-Leiterplatten auch bei geringerer Packungsdichte notwendig, z. B. um die induktionsarme Stromversorgung aller Bauteile zu gewährleisten.

Bauelemente auf und in Leiterplatten

[Bearbeiten | Quelltext bearbeiten]Einfache passive Bauelemente können in die Platine integriert werden. Induktivitäten, Spulen, kleine Kapazitäten, Kontakte oder Kühlkörper können direkt als Kupferschicht-Struktur ausgebildet werden. Widerstände werden teilweise mittels spezieller Pasten auf die Oberfläche oder in die verdeckten Layer eingedruckt. Dadurch werden in der Massenfertigung Bauelemente und Bestückung gespart.

Es gibt Platinen, auf oder in denen integrierte Schaltungen direkt platziert sind (Chip-On-Board-Technologie, kurz COB). Oft sind sie direkt zur Platine gebondet und nur durch einen Tropfen Kunstharz geschützt (englisch Glob Top).

Microvia-Technik

[Bearbeiten | Quelltext bearbeiten]Bei Multilayer-Platinen werden HDI-Leiterplatten (von engl. High Density Interconnect) angewendet. Dabei werden Sacklochbohrungen mit 50 µm bis 100 µm Durchmesser mittels Laser oder durch Plasmaätzen in die Außenlagen eingebracht und enden auf dem Kupfer der nächsten oder übernächsten Lage. Nach der Reinigung des verbliebenen Harzes werden diese Mikrobohrlöcher wiederum galvanisch verkupfert und somit elektrisch angebunden.

Bei Leiterplatten mit hoher Packungsdichte ist die Microvia-Technik notwendig, da wegen des Platzmangels und des geringen Abstandes der Kontakte nicht mehr alle Kontakte z. B. von Ball-Grid-Array-Bauteilen (BGA) elektrisch angebunden werden könnten. So bindet man die Pads der BGAs an Microviabohrungen an, die auf einer anderen Lage enden und gewährleistet so deren Entflechtung.

Buried-Via-Technik

[Bearbeiten | Quelltext bearbeiten]Die Vias (Durchkontaktierungen) verbinden auch hier zwei oder mehrere Kupferlagen, sind jedoch nur zwischen Innenlagen eingebracht und nicht von der Platinenoberfläche aus zugänglich. Buried Vias (dt. vergrabene Durchkontaktierungen) sind somit erst bei Multilayer-Platinen ab vier Lagen möglich.

Plugged-Via-Technik

[Bearbeiten | Quelltext bearbeiten]Neben Buried- und Micro-Vias besteht die Möglichkeit, Vias verschließen („pluggen“) zu lassen.[7] Mit dieser Technik können Vias direkt in SMD-Pads platziert werden, was z. B. bei BGA-Gehäusen mit kleinen Ballabständen die Entflechtung stark vereinfacht. Die Technik ist allerdings relativ teuer und wird nur selten genutzt, da die Oberfläche zusätzlich geschliffen und poliert werden muss, um überschüssiges Material abzutragen. Die verschiedenen Möglichkeiten, ein Via zu verschließen, sind spezifiziert in der Richtlinie IPC 4761.[8]

Dickkupfer

[Bearbeiten | Quelltext bearbeiten]Die Verwendung von Kupferstärken jenseits der üblichen Dicke von 35 µm (oft 200 µm bis 400 µm) wird als Dickkupfer bezeichnet. Sie erlauben höhere Strombelastbarkeiten und verbesserten lateralen Wärmetransport. Die Leiterzüge werden hierzu galvanisch verstärkt, die Genauigkeit ist eingeschränkt.

Eine Platine mit geringer Kupferdicke wird mit Fotolack bedeckt, invers belichtet und entwickelt. Nun liegen alle die Flächen frei, die Leiterzüge werden sollen. Nun wird galvanisch mit Kupfer verstärkt. Nachfolgendes Ätzen vermag dann ohne Abdecklack die Leiterzüge freizulegen, sodass nicht die gesamte Kupferdicke, sondern nur die dünne Grundschicht geätzt werden muss.

Eine Variante der Dickkupfertechnik ist die Eisbergtechnik (englisch iceberg technique). Dabei werden die noch geschlossenen in Folienform vorliegenden Kupferlagen photolithographisch vorstrukturiert: Bereiche, die kein Dickkupfer benötigen, werden dabei auf 20 µm oder 100 µm zurückgeätzt. Die Folien werden dann in das Prepreg eingepresst und konventionell weiterverarbeitet. Die partiell geringeren Erhebungen in Bereichen geringer Schichtdicke erlauben eine feinere Strukturierung und eine zuverlässigere Überdeckung mit Lötstopplack.

Wärmemanagement

[Bearbeiten | Quelltext bearbeiten]Thermal Vias haben keine elektrische Funktion, sie verbessern den Wärmetransport senkrecht zur Leiterplatte. Die Wärmeleitfähigkeit von Basismaterialien wie FR-4 ist mit 0,3 W/(m·K) für eine Entwärmung von Bauelementen oft zu gering. Thermal Vias nutzen die hohe Wärmeleitfähigkeit (300 W/(m·K)) von Kupfer, dem Material der Durchkontaktierung. Durch eine dichte Anordnung in einem Raster kann der Kupferanteil in die Leiterplatte wesentlich erhöht werden.

Metallkern (englisch metal core) und Dickkupfer erlauben eine höhere laterale Wärmeleitfähigkeit. Dazu werden Kupfer- oder Aluminiumbleche oder auf bis zu 400 µm verstärkte Kupferlagen in die Leiterplatte eingearbeitet.

Die Wärmeableitung durch Kühlmaßnahmen im Layout oder auch induktionsarme Durchkontaktierungen und Anschlüsse sind beim Löten jedoch ein Nachteil, weil dadurch der Wärmebedarf lokal stark erhöht ist. Sogenannte Thermal Pads, bei denen die Anbindung an kupfergefüllte Flächen gezielt geschwächt wird, dienen dazu, die Wärme in der Lötstelle zu halten und nicht in die Kupferfläche abzuleiten.

Flexible Leiterplatten

[Bearbeiten | Quelltext bearbeiten]Alternativ zu starren Leiterplatten finden auch dünne Flexleiterplatten bzw. Leiterfolien z. B. auf Basis von Polyimid-Folien Verwendung. Damit aufgebaute Baugruppen sind zwar teurer, können jedoch platzsparend durch Falten in engste Räume z. B. von Fotoapparaten, Videokameras oder Smartphones eingesetzt werden.

Flexible Verbindungen für dauernde Beanspruchung, z. B. in Tintenstrahldruckern, werden häufig ebenfalls als Polyimid-Folienleiterplatte ausgebildet.

- Starrflexible Leiterplatten

- Durch Kombination von flexiblen und starren Schichten beim Verpressen erhält man eine starrflexible Leiterplatte. Hier befinden sich z. B. Polyimid-Folien auf oder zwischen gewöhnlichen FR4-Schichten, die nach einer Tiefenfräsung Bereiche mit unterschiedlicher Dicke und Flexibilität ergeben. So lassen sich Stecker, Kabel und andere Verbindungselemente einsparen, allerdings entsteht damit auch die Notwendigkeit, bei Defekten das gesamte Starrflex-System auswechseln zu müssen.[9]

- Semiflexible Leiterplatten

- Wird nur ein nicht dauerhaft flexibler Bereich in der Leiterplatte benötigt, z. B. um die Montage bei begrenztem Platz zu ermöglichen, gibt es den Ansatz, den aus mehreren Prepregs (s. u.) aufgebauten Schichtstapel einer Leiterplatte bis auf wenige Lagen durch Fräsen oder vorgestanzte Prepregs mit ausgesparten Bereichen zu verjüngen. Der verjüngte Bereich wird typischerweise mit einer dauerflexiblen Lackschicht versehen und lässt sich dann wenige Male biegen.

Lötalternativen

[Bearbeiten | Quelltext bearbeiten]Als Alternative zum Verlöten der Bauteilanschlüsse auf einer Leiterplatte gibt es die Einpresstechnik. Dabei werden elastische oder starre Stifte in eng tolerierte und metallisierte Bohrungen der Leiterplatte gepresst. Aufgrund der plastischen Verformung der Partner ergeben sich sichere elektrische Verbindungen ohne Löten. Eine Anwendung sind vielpolige Stecker und Gewindebolzen.

Bei der Chip-On-Board-Technologie werden Chips ohne Gehäuse auf die Leiterplatte geklebt oder gelötet (Chipbonden) und direkt dort mittels Drahtbonden angeschlossen. Die auf Leiterplatten gebondeten Chips und Bonddrähte werden durch lichtabsorbierendes Kunstharz geschützt.

Oberflächenbehandlung und Ausrüstung

[Bearbeiten | Quelltext bearbeiten]Da zwischen der Leiterplattenproduktion und dem anschließenden Bestückprozess der elektronischen Bauelemente auf Leiterplatten im Regelfall Transport- und Lagerzeiten liegen, ist es notwendig, die Lötflächen aus blanken Kupfer, welche die Kontakte zu den elektronischen Bauelementen darstellen, vor Umwelteinflüssen wie Korrosion zu schützen, da andernfalls der Lötvorgang beeinträchtigt ist. Für die Oberflächenbehandlung finden folgende Verfahren bei Leiterplatten Anwendung:[10]

HAL

[Bearbeiten | Quelltext bearbeiten]Bei HAL, auch HASL für englisch Hot Air Solder Leveling, wird die fertige produzierte Leiterplatte in ein Bad aus flüssigem Zinn-Blei getaucht und nachfolgend mit heißer Luft das überschüssige Zinn-Blei auf der Oberfläche weggeblasen, um eine möglichst glatte Oberfläche an den Lötpads zu erhalten. Damit wird das Kupfer durch eine Schicht aus Zinn-Blei überzogen, welche auch dem herkömmlichen Lötzinn entspricht. HAL ist wegen der kostengünstigen Durchführung die am weitesten verbreitete Oberflächenbehandlung, weist aber als Nachteil durch ungleiche Verteilung der Zinn-Blei-Beschichtung an der Oberfläche relativ große Unebenheiten auf und kann bei sehr feinen Strukturen zu Kurzschlüssen führen.

Chemisch-Zinn

[Bearbeiten | Quelltext bearbeiten]Bei der Methode Chemisch-Zinn (englisch Immersion Tin) wird die oberste Schicht des Kupfers mit Hilfe von Thioharnstoff durch Zinn chemisch ausgetauscht. Der chemische Austausch von Kupferatomen durch Zinnatome endet von selbst, wenn die Kupferoberflächen auf der Leitplatte vollständig durch Zinn in einer Dicke von ca. 0,7 µm bis 1,2 µm abgedeckt sind. Der Vorteil von Chemisch-Zinn ist die sehr ebene Oberfläche und das Vermeiden von problematischen Stoffen wie Blei im Endprodukt. Die Nachteile sind der Aufwand und Kosten in der Fertigung, der Einsatz von krebserregendem Thioharnstoff und die Problematik, dass die reine Zinnoberfläche Whisker ausbilden kann.

OSP

[Bearbeiten | Quelltext bearbeiten]OSP, englisch Organic Solderability Preservative, ist eine Oberflächenbehandlung basierend auf organischen Substanzen wie Benzotriazol, Imidazol oder Benzimidazol, welche mit der obersten Kupferschicht eine einige 100 nm dicke metallorganische koordinative Bindung eingehen und so das Kupfer vor Oxidation schützen. Die OSP wird erst thermisch beim Lötprozess aufgelöst. Von Vorteil ist neben der ebenen Oberfläche die günstige Herstellung, nachteilig ist aber die begrenzte Lagerzeit. OSP sollte nicht bei Leiterplatten mit Durchsteckbauelementen eingesetzt werden, da die Oberflächenpassivierung in den Lötaugen nicht gewährleistet ist.

ENIG

[Bearbeiten | Quelltext bearbeiten]Bei ENIG, englisch Electroless Nickel Immersion Gold, wird zunächst eine ca. 3 µm bis 6 µm Schicht chemisch Nickel auf die Kupferoberfläche aufgebracht. Die Nickelschicht stellt eine Barriere für Gold zur Kupferschicht dar, da sonst das Gold in das Kupfer diffundieren würde. Auf die Nickelschicht wird eine ca. 50 nm bis 100 nm dicke Schicht chemisch Gold aufgebracht, dabei wird die oberste Nickelschicht durch Gold chemisch ausgetauscht. Der Vorteil dieser Methode ist auch neben der ebenen Oberfläche die vergleichsweise lange Lagerfähigkeit. Nachteilig ist der vergleichsweise hohe Prozessaufwand und damit verbundene Kosten. Des Weiteren führt die Goldbeschichtung der ENIG-Leiterplatten bei Wellenlöten zu einer Verunreinigung des Lötbades.

Normen und Vorschriften

[Bearbeiten | Quelltext bearbeiten]Zu dem Aufbau und den Eigenschaften von Leiterplatten gibt es vielfältige Vorschriften und Normen. Außer DIN-, IEC- und Normen des Institute for Printed Circuits (IPC) haben große Unternehmen teilweise auch eigene Werksnormen. Neben diesen universellen Normen gibt es für Rack-Systeme standardisierte Abmessungen für Leiterplatten:

- Europakarte (3 HE): 160 mm × 100 mm (DIN 41494 Teil 2), an der Schmalseite kontaktiert

- Doppeltes Europakarten-Format (6 HE): 233 mm × 160 mm, an der Breitseite kontaktiert.

Tests

[Bearbeiten | Quelltext bearbeiten]Leiterplatten werden oft noch vor der Auslieferung und Bestückung einer Prüfung unterzogen. Die visuelle Kontrolle (Auge oder digitale Bildverarbeitung) zwischen den einzelnen Fertigungsschritten (z. B. vor dem Aufbringen einer weiteren Lage) und am Ende der Fertigung ist bei den Leiterplattenherstellern meist im Preis inbegriffen.

Ein elektrischer Test am Ende der Herstellung ist meist kostenpflichtig und erfordert die kompletten CAD-Daten sowie einen Prüfautomaten, der sämtliche Signalwege kontaktiert und prüft. Bei den Prüfautomaten unterscheidet man zwischen dem In-Circuit-Tester und dem Flying-Prober. Die Flying-Prober haben mehrere einzelne Prüffinger, welche die Leiterplatten abtesten. Diese Technik hat den großen Vorteil, dass keine Adapter zum Kontaktieren benötigt werden und so auch kleine Serien günstig getestet werden können. Als Nachteil zählt die lange Prüfzeit zum Testen und dass mit diesem System meistens kein 100%iger Test durchgeführt wird (zu lange Prüfzeit). Beim In-Circuit-Tester werden die Leiterplatten mit Federstift-bestückten Adaptern oder sehr feinen sogenannten Starrnadeladaptern getestet. Diese Technik hat den Vorteil, dass alle Testpunkte auf einmal kontaktiert werden können und so ein sehr schneller Test mit einer 100%igen Prüftiefe erreicht werden kann. Die heutigen MCA-Microadapter (siehe Starrnadeladapter) ermöglichen mit dem Staggering das Kontaktieren von feinsten Strukturen der Mikroelektronik. Als Nachteil sind hier die hohen Adapterkosten zu erwähnen, die aber bei größeren Stückzahlen nicht mehr ins Gewicht fallen.

Fertig bestückte Leiterplatten können ebenfalls mit einem ICT-Testsystem geprüft werden, wofür oft zusätzliche Kontaktinseln layoutet werden, die im späteren Einsatz nicht mehr benötigt werden. Damit keine solchen zusätzlichen Testpunkte generiert werden müssen, kann auch hier ein Starrnadeladapter eingesetzt werden, der das Kontaktieren auf Bauteilanschlüsse, Stecker oder sogar Chips ermöglicht.

Oft wird nur eine optische (Bilderkennungssoftware) und/oder Funktionskontrolle am Ende der Fertigung (d. h. nach der Bestückung) durchgeführt, da die Herstellungstechnologie der Leiterplatten selbst sehr viel zuverlässiger als nachfolgende Verfahrensschritte ist.

Durchgangstest

[Bearbeiten | Quelltext bearbeiten]

Beim Durchgangstest wird die Leiterplatte auf fehlerhafte und fehlende Verbindungen getestet. Diese Unterbrechungen können durch mechanische Beschädigungen oder durch Filmfehler beim Belichten entstehen.

- Funktionsweise

- Beim Durchgangstest werden alle zu einem Netz gehörenden Punkte gegeneinander getestet. Bei Einzelpunkten kann keine Verbindung geprüft werden.

Durch Schmutz auf den Kontaktierstellen können die Messungen ein hochohmiges Ergebnis zeigen. Mögliche Verschmutzungen sind: Staub, Fräsrückstände oder Oxidation auf der Kontaktierfläche. Durch ein erneutes Kontaktieren (Retest) können diese Phantomfehler (Fehler, die nicht existieren) oft ausgeschlossen werden.

Die Messresultate werden bei zweipoliger Messung produktspezifisch z. B. folgendermaßen klassifiziert:

(Messschwellen sind teilespezifisch zu definieren)

- Messung < 10 Ω → Gute Verbindung

- Messung > 10 Ω → Hochohmige Verbindung

- Messung > 2 MΩ → Unterbrechung

Für Messungen von Verbindungen oder Widerständen unter 10 Ω muss oft eine Vierleitermessung eingesetzt werden, dadurch verfälschen die Kabel- und Kontaktwiderstände das Messresultat nicht.

Kurzschlusstest

[Bearbeiten | Quelltext bearbeiten]Ein Kurzschluss ist eine Verbindung zwischen zwei Punkten, die entsprechend der Schaltung nicht bestehen darf. Kurzschlüsse sind Verbindungen, die z. B. durch Zinnfäden, schlechtes Ätzen oder mechanische Beschädigung der Isolationsschicht zwischen den Lagen hervorgerufen werden.

- Funktionsweise

- Für jedes Netz wird ein Testpunkt als Primärtestpunkt festgelegt. Danach wird zwischen allen Netzen die Isolation gemessen.

Wenn eine Leiterplatte 3 Netze hat, wird Netz 1 gegen Netz 2, Netz 1 gegen Netz 3 und Netz 2 gegen Netz 3 gemessen. Sind weitere Netze vorhanden, verhalten sich die Anzahl Messungen nach:

- 2 Netze = 1 Messung

- 3 Netze = 3 Messungen

- 4 Netze = 6 Messungen

- 5 Netze = 10 Messungen

- 6 Netze = 15 Messungen

- N Netze = N·(N-1)/2 Messungen

Wird beim Durchgangstest eine Unterbrechung festgestellt, wird dort ein weiterer Primärpunkt gesetzt und ein weiteres Sub-Netz generiert (Netz 3a). So kann die Leiterplatte zu 100 % auf Kurzschlüsse getestet werden.

Die Messresultate werden produktspezifisch zum Beispiel folgendermaßen interpretiert:

- Messung > 2 MΩ → Kein Kurzschluss

- Messung < 2 MΩ → Hochohmiger Kurzschluss

- Messung < 100 Ω → Kurzschluss

Röntgentest

[Bearbeiten | Quelltext bearbeiten]

Vor allem bei mehrlagigen Platinen werden auch Röntgenaufnahmen eingesetzt, um eine visuelle Prüfung durchführen zu können, zum Beispiel der Passgenauigkeit der verschiedenen Lagen.

Belastung von Leiterbahnstrukturen mit großen Strömen

[Bearbeiten | Quelltext bearbeiten]Häufig, besonders in Dickschicht-Hybridtechnik, besteht die Notwendigkeit, unbestückte Leiterplatten mit größerem Prüfstrom auf Einengungen, schlechte Durchkontaktierungen usw. zu testen. Solche Fehlerstellen werden dann zerstört und können als Unterbrechung erkannt werden. Ein zerstörungsfreies Mittel zur Prüfung von Leiterplatten auch im Betrieb ist die Thermografie.

Basismaterial

[Bearbeiten | Quelltext bearbeiten]

Einfache Leiterplatten bestehen aus einem elektrisch isolierenden Trägermaterial (Basismaterial), auf dem eine oder zwei Kupferschichten aufgebracht sind. Die Schichtstärke beträgt typischerweise 35 µm und für Anwendungen mit höheren Strömen zwischen 70 µm und 140 µm. Um dünnere Leiterbahnen zu ermöglichen, werden auch Leiterplatten mit nur 18 µm Kupfer hergestellt. In englischsprachigen Ländern wird manchmal statt der Schichtstärke die Masse der leitfähigen Schicht pro Flächeneinheit in Unzen pro Quadratfuß (oz/sq.ft) angegeben. In diesem Fall entspricht 1 oz/sq.ft etwa 35 µm Schichtstärke.

Leiterplatten waren früher meist Hartpapier mit der Materialkennung FR2. Heute werden außer für billige Massenartikel meist mit Epoxidharz getränkte Glasfasermatten mit der Materialkennung FR4 verwendet. FR4 hat eine bessere Kriechstromfestigkeit und bessere Hochfrequenzeigenschaften sowie eine geringere Wasseraufnahme als Hartpapier.

Durch die Glasfasermatten hat FR4 eine anisotrope Struktur, was sich unter anderem in den Längenausdehnungskoeffizienten ausdrückt, die senkrecht zur Leiterplatte 50–60 ppm/K (bis 100 °C) beträgt, in X- und Y-Richtung ca. 18 bzw. 14 ppm/K, also ähnlich zu den aufgebrachten Kupferbahnen (17 ppm/K).[11]

Für Spezialanwendungen kommen auch andere Materialien als Basismaterial zum Einsatz. Beispiele sind Teflon, Aluminiumoxid oder Keramik in LTCC und HTCC für die Hochfrequenztechnik sowie Polyesterfolie für flexible Leiterplatten. Hersteller dieser speziellen Basismaterialien sind Firmen wie Rogers Corporation und Arlon Materials for Electronics, wovon sich auch die umgangssprachliche Bezeichnung „Rogers“ bzw. „Arlon“ im technischen Englischen für teflonbasierende Leiterplatten mit Anwendungsbereich in der Hochfrequenztechnik ableitet.

Für Leiterplatten mit hohen Anforderungen an die Wärmeabführung werden Basismaterialien mit Metallkernen wie Aluminium oder Kupfer verwendet, z. B. im Bereich der Beleuchtungstechnik mit Hochleistungsleuchtdioden. Diese Trägermaterialien werden auch als Direct Bonded Copper oder als Insulated metal substrate (IMS) bezeichnet.

Bei Anwendungen für niedrige Temperaturen oder hohe Luftfeuchtigkeit können auch Basismaterialien mit integrierten Heizelementen eingesetzt werden, die Unterkühlen oder Betauung der Schaltung verhindern. Zudem wird an alternativen Materialien geforscht, die umweltfreundlicher sind, aktuell gibt es dort aber noch Probleme mit der Feuchteresistenz.

Parameter verschiedener Materialien

[Bearbeiten | Quelltext bearbeiten]| Bezeichnung | Verstärkung | Matrix | Kosten rel. zu FR4 |

Erweichungspunkt TG 1 (°C) |

max. Betriebs- temperatur 2 (°C) |

Dielektrizi- tätszahl εr |

Isolations- widerstand |

Kriechstrom- verhalten |

Verlustwinkel (Grad) |

|---|---|---|---|---|---|---|---|---|---|

| FR2 | Papier | Phenolharz | 30 % | 80 | 70 | 4,25 | − − | − − | 0,05 bei ? MHz |

| FR3 | Papier | Epoxidharz (Epoxy) | 60 % | 100 | 90 | + − | + − | 0,041 bei ? MHz | |

| CEM1 | Papier | Epoxy | 70 % | 105 | + − | + − | 0,031 bei ? MHz | ||

| CEM3 | Glasvlies | Epoxy | 80 % | 120 | + | + | |||

| FR4 Standard | Glasfasergewebe | Di/Tetra-Epoxy | 100 % | 125–150 | 115–140 | 3,8–4,5 | + | + | 0,019 bei ? MHz |

| FR4 Halogenfrei | Glasfasergewebe | Di/Tetra-Epoxy | 130 % | 125–180 | 115–170 | 3,8–4,5 | + | + | 0,019 bei ? MHz |

| FR5 | Glasfasergewebe | Tetra/Multi-Epoxy | 150 % | 150–185 | 140–175 | 0,016 bei ? MHz | |||

| FR5 BT | Glasfasergewebe | BT-Epoxy | 300 % | 190–240[12][13] | |||||

| Polyimid | ohne oder mit Glasfasern | Polyimid | 332–438 % | 240–270 | 230–260 | + | + | ||

| Teflon (PTFE) | ohne oder mit Glasfasern | 800 % | 260–320 | 250–310 | 2–2,28 | + + | + + | 0,0009 (10 GHz)[14] ...0,03 (10 GHz)[14] | |

| Keramik (Aluminiumoxid) |

– | 800 % | nicht relevant | nicht relevant | 7 (4,5–8,4[15] 8[16]) |

+ + | + + |

Basismaterialherstellung

[Bearbeiten | Quelltext bearbeiten]In der Imprägnieranlage werden zunächst das Grundharz, Lösungsmittel, Härter, Beschleuniger gemischt. Dem können noch andere Stoffe zugesetzt werden, wie z. B. Farbpigmente, Flammschutzmittel und Flexibilisatoren. Die Trägerstoffe (z. B. Papier, Glasgewebe, Aramidgewebe) werden in Rollen angeliefert, so dass der Prozess fortlaufend durchgeführt werden kann. Nachdem der Träger über Umlenkrollen durch das Bad gezogen wurde (Tränkung), wird das Material im Ofen getrocknet. Dabei verdunstet nicht nur das Lösungsmittel, sondern auch das Harz erreicht durch die Wärmezufuhr einen Zwischenzustand – das Harz härtet noch nicht vollständig aus, bei erneuter Wärmezufuhr wird es zunächst wieder klebrig und härtet erst dann aus. Dieses Halbzeug aus Harz und Träger nennt man Prepreg. Es wird zur Herstellung der Leiterplatten verwendet, indem die Lagen unter Wärmeeinfluss verpresst werden. Bei Multilayer-Leiterplatten werden mehrere Schichten Basismaterial und Kupfer nacheinander verpresst und geätzt.

Verbindungen

[Bearbeiten | Quelltext bearbeiten]Mechanische Verbindungen

[Bearbeiten | Quelltext bearbeiten]Bei der Montage von Platinen in einem Gehäuse muss zwischen der ggf. metallenen Montagebasis und der Platine ein Abstand sichergestellt werden. Zum einen, damit keine Kurzschlüsse entstehen, zum anderen, damit die unebene Unterseite der Platine mit den vielen Lötpunkten und teilweise hervorstehenden Drahtenden nicht direkt aufliegt, was zu mechanischen Spannungen führen würde. Dazu verwendet man u. a. lange Gewindeschrauben mit Abstandshaltern und Muttern oder Kunststoffelemente, die in Löcher in der Platine und auf der anderen Seite im Gehäuse eingeklipst werden. Manchmal übernimmt auch die im Folgenden beschriebene elektrische Verbindung den mechanischen Part mit.

Elektrische Verbindungen

[Bearbeiten | Quelltext bearbeiten]Wenn die Leiterplatte eine Steckkarte ist, die auf einer anderen Leiterplatte sitzt, verwendet man meist direkte Steckverbinder und Federleisten.

Andere vielpolige Kabelverbindungen werden über Leitgummi oder über Steckerleisten und Stiftleisten realisiert, wobei die Kontakte in einer oder auch mehreren Reihen angeordnet sein können. Wenn es nur um wenige Pole geht, werden auch Federleisten oder kleine Buchsen- oder Kupplungsteile auf Lötstifte aufgesteckt.

In speziellen Umgebungen wie beispielsweise innerhalb mechanischer Fotoapparate wählt man Folienverbinder, die praktisch biegsame Leiterplatten darstellen, ggf. mit direkten Steckverbindern an einem oder beiden Enden oder alternativ direkter Verlötung.

Recycling

[Bearbeiten | Quelltext bearbeiten]Leiterplatten enthalten einen hohen Anteil Kupfer und Edelmetallen, dessen Wiedergewinnung durch die Fortschritte bei Recycling-Verfahren wirtschaftlich geworden ist:[17]

| Element | Mobiltelefone | Computer | Mischfraktion |

|---|---|---|---|

| Kupfer | 34,49 | 20,19 | 20,1 |

| Aluminium | 0,26 | 5,7 | 13,5 |

| Eisen | 10,57 | 7,33 | 7,09 |

| Zink | 5,92 | 4,48 | 2,18 |

| Blei | 1,87 | 5,53 | 1,16 |

| Zinn | 3,39 | 8,83 | 0,62 |

| Nickel | 2,63 | 0,43 | 0,73 |

| Silber | 0,21 | 0,16 | 0,027 |

| Gold | 0,03[18] | 0,13 | 0,003 |

Literatur

[Bearbeiten | Quelltext bearbeiten]- Günther Hermann (Hrsg.): Handbuch der Leiterplattentechnik – Laminate – Manufacturing – Assembly – Test. 2. Auflage. Eugen G. Leuze Verlag, Saulgau/Württ. 1982, ISBN 3-87480-005-9.

- Günther Hermann (Hrsg.): Handbuch der Leiterplattentechnik – Band 2: Neue Verfahren, neue Technologien. Eugen G. Leuze Verlag, Saulgau/Württ. 1991, ISBN 3-87480-056-3.

- Günther Hermann (Hrsg.): Handbuch der Leiterplattentechnik – Band 3: Leiterplattentechnik, Herstellung und Verarbeitung, Produkthaftung, Umweltschutztechnik mit Entsorgung. Eugen G. Leuze Verlag, Saulgau/Württ. 1993, ISBN 3-87480-091-1.

- Günther Hermann (Hrsg.): Handbuch der Leiterplattentechnik – Band 4: Mit 112 Tabellen. Eugen G. Leuze Verlag, Saulgau/Württ. 2003, ISBN 3-87480-184-5

- H.-J. Hanke (Hrsg.): Baugruppentechnologie der Elektronik – Leiterplatten. Technik Verlag, Berlin 1994, ISBN 3-341-01097-1.

- Daniel Schöni (Hrsg.): Schaltungs- und Leiterplattendesign im Detail – Von der Idee zum fertigen Gerät. BoD Books on Demand, Norderstedt 2017, ISBN 978-3-7392-1871-7.

Siehe auch

[Bearbeiten | Quelltext bearbeiten]Weblinks

[Bearbeiten | Quelltext bearbeiten]- Günstige Platinenherstellung mit einfachen Mitteln

- Platinen mit der „Direkt-Toner-Methode“ ätzen

- Funktionsprinzip der Bestückungstechnologien (SMD, BGA, THT) bildlich erklärt.

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Stoffströme bei der Herstellung von Leiterplatten. ( vom 15. Januar 2015 im Internet Archive) (PDF; 729 kB) Forschungszentrum Karlsruhe 1996.

- ↑ Paul Eisler, Harold Vezey Strong: "639,178 (A) Manufacture of electric circuits and circuit components".

- ↑ Andus Electronic Leiterplatten Strombelastbarkeit auf Leiterplatten ( vom 3. Dezember 2013 im Internet Archive) Grundlagen und Praxiswissen.

- ↑ Eilhard Haseloff: EMV-gerechte Gerechte Gestaltung vom Leiterplatten, Texas Instruments Deutschland, Applikationslabor, Publikation EB215, Mai 1993

- ↑ Lotpasten Dosierung, Mitteilung der Firma Fritsch GmbH, abgerufen am 19. Feb. 2021.

- ↑ microcirtec.de.

- ↑ Design Regeln Pluggen (PDF; 272 kB)(PDF) ILFA Feinstleitertechnik; mit Prozessbeschreibung und Abbildungen.

- ↑ Via Abdeckung – Spezifikation nach IPC 4761. Multi CB Leiterplatten; mit Abbildungen.

- ↑ Schaltungs- und Leiterplattendesign im Detail. Abgerufen am 22. April 2017.

- ↑ Al Wright: Printed Circuit Board Surface Finishes – Advantages and Disadvantages. Abgerufen am 9. Juli 2016.

- ↑ Analyse mit DDK, TMA und TGA-EGA. In: USER COM 1/99. Ehemals im (nicht mehr online verfügbar); abgerufen am 18. Januar 2020. (Seite nicht mehr abrufbar. Suche in Webarchiven)

- ↑ Alternative board materials. ( vom 15. Mai 2008 im Internet Archive) (englisch)

- ↑ High Tg (Glass Transition Temperature). Unicircuit.

- ↑ a b mauritz-hamburg.de ( vom 22. Oktober 2014 im Internet Archive) Duorid 5880, glasfaserverstärkt.

- ↑ Grundlagen der Radartechnik zur Füllstandmessung ( vom 26. Oktober 2007 im Internet Archive), 9

- ↑ quick-ohm.de ( vom 24. Mai 2010 im Internet Archive).

- ↑ Luciana Harue Yamane, Viviane Tavares de Moraes, Denise Crocce Romano Espinosa, Jorge Alberto Soares Tenório: Recycling of WEEE: Characterization of spent printed circuit boards from mobile phones and computers. In: Waste Management. Band 31, Nr. 12, Dezember 2011, S. 2553–2558, doi:10.1016/j.wasman.2011.07.006.

- ↑ Landesamt für Natur, Umwelt und Verbraucherschutz Nordrhein-Westfalen: Recycling kritischer Rohstoffe aus Elektronik-Altgeräten, Fachbericht 2012, Seite 41, abgerufen am 8. Juni 2023