Arm Cortex-A

Arm Cortex-A (in älterer Schreibweise vor August 2017 ARM Cortex-A) bezeichnet eine Serie von Mikroprozessordesigns des Unternehmens ARM Holdings Plc, die zur Ausführung komplexer Rechenaufgaben vorgesehen sind und als IP-Core Lizenznehmern angeboten werden. Der Zusatz „A“ steht für applications (dt. Anwendungen) und soll die so bezeichneten Prozessoren als geeignete Hardwarebasis für die Ausführung komplexer Betriebssysteme und unterschiedlicher Softwareanwendungen ausweisen. Die CPUs basieren auf der Arm-Architektur und implementieren den Befehlssatz (engl. Instruction Set Architecture, ISA) ARMv7-A, ARMv8-A oder ARMv9-A. Die IP-Cores der Arm Cortex-A-Serie werden als energieeffiziente Hochleistungsplattform beworben und weltweit von zahlreichen Chipherstellern zum Entwurf eigener Ein-Chip-Systeme lizenziert. Entsprechende SoCs kommen unter anderem in Smartphones, mobilen Computern, digitalen Fernsehern und Settopboxen zum Einsatz. Ein Semi-Custom-Programm ermöglicht es Kunden ein Core-Design von Arm den eigenen Bedürfnissen anpassen zu lassen.

Arm Cortex-A8

[Bearbeiten | Quelltext bearbeiten]

Im Vergleich mit seinem Vorgänger ARM11 handelt es sich bei dem 2005 vorgestellten[1] Cortex-A8 um ein 32-bit superskalares Single-Core-Dual-Issue-Design, das rund die doppelte Anzahl Instruktionen pro Taktzyklus ausführen kann. Er kommt auf eine Rechenleistung von 2,0 DMIPS/MHz und besitzt jeweils 32 kB L1-Cache für Befehle und Daten sowie einen 512 kB großen L2-Cache. Die Taktfrequenzen in einem 65-nm-Prozess von TSMC bewegen sich zwischen 600 MHz und mehr als 1 GHz. Die Pipeline-Länge beträgt 13 Stufen.[2]

Der Cortex-A8 war der erste Core aus der Cortex-Familie, der in zahlreichen Geräten der Unterhaltungselektronik implementiert wurde.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- NEON SIMD-Erweiterungen

- VFPv3-Gleitkommaeinheit

- Thumb-2-Befehlssatz

- Jazelle RCT

- dynamische Sprungvorhersage mit mehr als 95 % Trefferquote

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementiertem Cortex-A8-Core umfassen u. a.:

- Allwinner Tech A10/A13/A10s/R8

- Apple A4

- Freescale Semiconductor i.MX50, i.MX51 und i.MX53

- Rockchip RK2918, RK2906

- Samsung Exynos 3110

- Texas Instruments OMAP3

- Texas Instruments Sitara (BeagleBone)

- Conexant CX92755

Arm Cortex-A9

[Bearbeiten | Quelltext bearbeiten]

Der 2007 vorgestellte[3] Arm Cortex-A9 ist ein 32-bit-Mikroprozessor, der die Armv7‑A-Architektur implementiert. Er kann 32-bit-ARM-Befehle, 16- und 32-bit-Thumb-Befehle und 8-bit Java-Bytecodes ausführen. Beim Cortex-A9 handelt sich um ein superskalares Dual-Issue-Out-of-Order-Design. Der Prozessor kommt auf eine Rechenleistung von 2,5 DMIPS/MHz und besitzt jeweils 32 kB L1-Cache für Befehle und Daten sowie einen 128 kB bis 8 MB großen L2-Cache. Die Taktfrequenzen in einem 45-nm-Prozess von TSMC bewegen sich zwischen 800 MHz und 2 GHz. Die Pipeline-Länge beträgt 8 Stufen.[2] Der Cortex-A9 ist der erste Vertreter aus der Cortex-A-Familie, der sowohl in Uniprozessor- als auch Multiprozessorkonfigurationen eingesetzt werden kann.[3] Der Multiprozessor Arm Cortex-A9 MPCore verfügt über bis zu vier Cache-kohärente Cortex-A9-Prozessorkerne, die unter der Kontrolle der Snoop Control Unit (SCU) stehen. Die SCU stellt die L1-Data-Cache-Kohärenz sicher.[4]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- NEON SIMD-Erweiterungen (optional)[5]

- VFPv3-Gleitkommaeinheit

- Thumb-2-Befehlssatz

- TrustZone-Sicherheitserweiterungen

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT.

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementierten Cortex-A9-Cores umfassen u. a.:

- Altera SoC FPGA

- AMLogic AML7366-M6C, AML8726-Familie, M801, M802, S802, S812, T866, T868

- Apple A5, A5X

- Broadcom BCM11311 (Persona ICE)

- Calxeda EnergyCore ECX-1000

- Entropic EN7588

- Freescale Semiconductor i.MX6

- HiSilicon K3V2 -Hi3620

- Marvell 88DE3005-A1

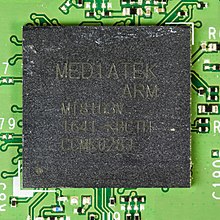

- MediaTek MT6575 (Single-Core), MT6577 (Dual-Core)

- Nufront NuSmart 2816, 2816M, 115

- Nvidia Tegra 2, 3, 4i

- Renesas EMMA Mobile/EV2

- Rockchip RK3026, RK3066, RK3168, RK3188(T), RK2926, RK2928

- Samsung Exynos 4210, 4212, 4412

- Sony CXD5315GG (SoC der PlayStation Vita)

- STMicroelectronics SPEAr1310, SPEAr1340

- ST-Ericsson Nova A9500, NovaThor U8500, NovaThor U9500

- Texas Instruments OMAP4

- Trident Microsystems 847x/8x/9x

- WonderMedia WM8850, WM8950 und WM8980

- Xilinx Zynq Extensible Processing Platform

- ZiiLABS ZMS-20

Arm Cortex-A5

[Bearbeiten | Quelltext bearbeiten]

Der 2009 vorgestellte[6] Arm Cortex-A5 MPCore ist ein 32-bit-Multicore-Prozessor mit bis zu 4 Cache-kohärenten Cortex-A5-Cores, welche jeweils den Armv7-A-Befehlssatz implementieren. Es handelt sich um ein Single-Issue-In-Order-Design. Er kommt auf eine Rechenleistung von 1,57 DMIPS/MHz und besitzt jeweils 4-64 kB L1-Cache für Befehle und Daten sowie optional einen 16 kB bis 1 MB großen L2-Cache. Die Taktfrequenzen in einem 40-nm-Prozess von TSMC erreichen bis zu 1 GHz. Die Pipeline-Länge beträgt 8 Stufen.[2] Der Cortex-A5 wurde als energieeffizienterer Nachfolger der ARM9- und ARM11-Cores für Einsteiger- und Mittelklasse-Mobilgeräte vorgestellt. Im Vergleich zu diesen älteren Cores bietet der Cortex-A5 den Vorteil des moderneren Befehlssatzes Armv7 gegenüber ARMv4/v5 (ARM9) bzw. ARMv6 (ARM11) sowie VFPv3 und NEON-SIMD-Erweiterungen.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- NEON-SIMD-Erweiterungen

- VFPv3-Gleitkommaeinheit

- Thumb-2-Befehlssatz

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementierten Cortex-A5-Cores umfassen u. a.:

- Microchip SAMA5D3

- Freescale Vybrid Series

- Qualcomm Snapdragon MSM8225

- Spreadtrum SC8810

- Actions Semiconductor ATM7029

- AMD Fusion APUs (Cortex-A5 als Sicherheits-Koprozessor)

- Yaskawa ANTAIOS[7]

Arm Cortex-A15

[Bearbeiten | Quelltext bearbeiten]Der 2010 vorgestellte[8] Arm Cortex-A15 MPCore ist ein 32-bit-Multicore-Prozessor mit bis zu 4 Cache-kohärenten Cortex-A15-Cores, welche jeweils den Armv7-A-Befehlssatz implementieren. Es handelt sich um ein 3-Wege-superskalares Out-of-Order-Design. Er kommt auf eine Rechenleistung von 3,4 DMIPS/MHz und besitzt jeweils 32 kB L1-Cache für Befehle und Daten sowie einen 128 kB bis 2 MB großen L2-Cache. Die Taktfrequenzen in einem 28-nm-Prozess von TSMC erreichen bis zu 2,5 GHz. Die Pipeline-Länge beträgt 15 Stufen.[9] Beim Big.LITTLE-Prozessing wird ein Cluster bestehend aus Cortex-A15-Cores aus Energiespargründen mit einem Cluster von 1 bis 4 Cortex-A7 zusammen auf einem Chip implementiert, die jeweils abwechselnd je nach Anforderungen der Software an die Rechenleistung diese abarbeiten.[10]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- 40-bit großer physischer Adressraum für bis zu 1 TB RAM, pro Prozess ist jeweils ein 32-bit-Adressraum ansprechbar

- 4 Cores pro Cluster, bis zu 2 Cluster pro Chip mit CoreLink 400 (eine AMBA-4-kohärente Schaltmatrix)

- DSP- und NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz

- TrustZone-Sicherheitserweiterungen

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementierten Cortex-A15-Cores umfassen u. a.:

- Broadcom SoC

- HiSilicon K3V3

- Nvidia Tegra 4, K1

- Renesas MP6530, R-H2

- Samsung Exynos-5210, Exynos Octa

- ST-Ericsson Nova A9600

- Texas Instruments OMAP5

- Annapurna Alpine AL-212, AL-314, AL-514, AL-5140, AL-21400

Arm Cortex-A7

[Bearbeiten | Quelltext bearbeiten]

Der 2011 vorgestellte[11] Arm Cortex-A7 MPCore ist ein 32-bit-Multicore-Prozessor, der den Armv7-A-Befehlssatz implementiert. Es handelt sich um ein teilweises Dual-Issue-In-Order-Design. Er kommt auf eine Rechenleistung von 1,9 DMIPS/MHz und besitzt zwei separate, 8-64 kB große L1-Caches sowie optional einen 128 kB bis 1 MB großen L2-Cache. Die beiden L1-Caches dienen dazu, Befehle und Daten voneinander unabhängig zwischenzuspeichern.[12] Die Pipeline-Länge beträgt 8 Stufen.[10] Die Taktfrequenzen in einem 28-nm-Prozess von TSMC erreichen beim Lizenznehmer Mediatek bis zu 2 GHz.[13] Seitens ARM sind bis zu 4 Prozessorkerne pro Cluster vorgesehen, durch die AMBA 4 Technologie lassen sich mehrere kohärente SMP-Cluster miteinander kombinieren. Der Cortex-A7 tritt sowohl alleine als energieeffizienterer Nachfolger des Cortex-A8 als auch beim Big.LITTLE-Prozessing in Erscheinung. Hier wird ein Cluster bestehend aus 1-4 Cortex-A7-Cores aus Gründen einer höheren Rechenleistung mit einem Cluster von 1 bis 4 Cortex-A15 zusammen auf einem Chip implementiert, die jeweils abwechselnd je nach Anforderungen der Software an die Rechenleistung diese abarbeiten.[10]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- 40-bit großer physischer Adressraum für bis zu 1 TB RAM, pro Prozess ist jeweils ein 32-bit-Adressraum ansprechbar

- 4 Cores pro Cluster, bis zu 2 Cluster pro Chip mit CoreLink 400 (eine AMBA-4-kohärente Schaltmatrix)

- DSP- und NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz

- TrustZone-Sicherheitserweiterungen

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementierten Cortex-A7-Cores umfassen u. a.:

- Allwinner A20, A31, A31s, H3, H2+

- Broadcom BCM2836 (Raspberry Pi 2 Model B)

- Freescale Semiconductor i.MX7

- HiSilicon K3V3

- Marvell PXA1088

- Mediatek MT6589

- Qualcomm Snapdragon S4 Play MSM8226 und MSM8626

- STMicroelectronics STM32MP1

Arm Cortex-A53

[Bearbeiten | Quelltext bearbeiten]

Der 2012 vorgestellte Arm Cortex-A53 MPCore ist ein 64-bit-Multicore-Prozessor mit bis zu 4 Cache-kohärenten Cortex-A53-Cores, welche jeweils den Armv8-A-Befehlssatz implementieren. Es handelt sich um ein teilweises Dual-Issue-In-Order-Design. Er kommt auf eine Rechenleistung von 2,3 DMIPS/MHz und besitzt jeweils 8-64 kB L1-Cache für Befehle und Daten sowie optional einen 128 kB bis 2 MB großen L2-Cache. In einem SoC-Entwurf des Herstellers MediaTek, produziert im 16nm-FinFET+-Verfahren, erreicht der Prozessor eine Taktfrequenz von bis zu 2,6 GHz.[14] Die Pipeline-Länge beträgt 8 Stufen.[15] Der Cortex-A53 tritt sowohl alleine als auch beim Big.LITTLE-Prozessing in Erscheinung. Hier wird ein Cluster, bestehend aus einem bis vier Cortex-A53-Cores, aus Gründen einer höheren Rechenleistung mit einem Cluster von einem bis vier Cortex-A57 zusammen auf einem Chip implementiert, die jeweils abwechselnd je nach Anforderungen der Software an die Rechenleistung diese abarbeiten.[10]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.0-A

- Betriebsmodi AArch64 (64-bit) und AArch32 (32-bit und Armv7-Rückwärtskompatbilität)

- 40-bit großer physischer Adressraum für bis zu 1 TB RAM, pro Prozess ist jeweils ein 32-bit-Adressraum ansprechbar

- erweiterte NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Hardware-Verschlüsselungen (AES, SHA-1, SHA2-256)

- Unterstützung von Hardware-Virtualisierung

- TrustZone-Sicherheitserweiterungen

- Thumb-2-Befehlssatz

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

Chips

[Bearbeiten | Quelltext bearbeiten]

Die System-on-Chips (SoC) mit implementierten Cortex-A53-Cores umfassen u. a.:

- Allwinner A64, H5, H6

- Amlogic S805X, S905(L/X/D/W/Z), S905X2, S905Y2, S912, S922X, A112, A113, A311D

- Broadcom BCM2837 (Raspberry Pi 2 Model B v1.2 und 3 Model B), BCM2837B0 (Raspberry Pi 3 Model A+ und B+)

- HiSilicon Kirin 620, 650, 655, 658, 710, 930, 935, 950, 955, 960, 970

- Mediatek MT6732, MT6735, MT6750, MT6752, MT6753, MT6755, MT6757, MT6795, MT6797(T), MT6799, MT8165, MT8173(C), MT8176, MT8732, MT8735, MT8752

- Rockchip RK3368, RK3399

- Samsung Exynos 5433, 7420, 7570, 7578, 7580, 7870, 7880, 8890, 8895

- Qualcomm Snapdragon 410, 415, 420, 425, 430, 435, 610, 615, 616, 617, 625, 630, 650, 652, 808 und 810

- Xilinx Zynq UltraScale+ MPSoC

Arm Cortex-A57

[Bearbeiten | Quelltext bearbeiten]Der ebenfalls 2012 vorgestellte Arm Cortex-A57 MPCore ist ein 64-bit-Multicore-Prozessor mit bis zu 4 Cache-kohärenten Cortex-A57-Cores, welche jeweils den Armv8-Befehlssatz implementieren. Es handelt sich um ein 3-Wege-superskalares Out-of-Order-Design. Er kommt auf eine Rechenleistung von 4,1 DMIPS/MHz und besitzt jeweils 48/32 kB L1-Cache für Befehle bzw. Daten sowie einen 512 kB bis 2 MB großen L2-Cache. Die Taktfrequenzen in einem 20-nm-Prozess von TSMC werden 2,5 GHz erreichen. Die Pipeline-Länge beträgt 15 Stufen.[15] Beim Big.LITTLE-Prozessing wird ein Cluster bestehend aus Cortex-A57-Cores aus Energiespargründen mit einem Cluster von 1 bis 4 Cortex-A53 zusammen auf einem Chip implementiert, die jeweils abwechselnd je nach Anforderungen der Software an die Rechenleistung diese abarbeiten.[10]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.0-A

- Betriebsmodi AArch64 (64-bit) und AArch32 (32-bit und Armv7-Rückwärtskompatbilität)

- 4 Cores pro Cluster (AMBA-4 ACE und AMBA-5 CHI wird unterstützt)

- 44-bit großer physischer Adressraum

- erweiterte NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Hardware-Verschlüsselungen (AES, SHA-1, SHA2-256)

- Unterstützung von Hardware-Virtualisierung

- TrustZone-Sicherheitserweiterungen

- Thumb-2-Befehlssatz

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementierten Cortex-A57-Cores umfassen u. a.:

- Broadcom BCM5871X (communication processors)

- Nvidia TX2

- Samsung Exynos 5433

- Qualcomm Snapdragon 808 und 810

Arm Cortex-A12/A17

[Bearbeiten | Quelltext bearbeiten]

Der 2013 vorgestellte Arm Cortex-A12 MPCore ist ein 32-bit-Multicore-Prozessor mit bis zu 4 Cache-kohärenten Cortex-A12-Cores, welche jeweils den Armv7-A-Befehlssatz implementieren. Es handelt sich um ein Dual-Issue-Out-of-Order-Design. Er kommt auf eine Rechenleistung von 3,0 DMIPS/MHz und besitzt einen 32-64 kB L1-Cache für Befehle, einen 32 kB großen L1-Cache für Daten sowie einen 256 kB bis 8 MB großen L2-Cache. Die Taktfrequenzen in einem 28-nm-Prozess von TSMC erreichen bis zu 2 GHz. Die Pipeline-Länge beträgt 10 Stufen. Der Cortex-A12 sollte die Nachfolge des Cortex-A9 antreten und wurde für eine Fertigung in einer Strukturgröße von 28 nm entwickelt. Die höhere Rechenleistung/MHz (3,0 statt 2,5 DMIPS/MHz) wurde u. a. durch ein komplexeres Out-of-Order-Design, eine größere Sprunghistorien-Tabelle, mehr Ausführungseinheiten (7 statt 3) und einen voll integrierten L2-Cache erreicht.[16] Zum Zeitpunkt der Vorstellung sollte das Prozessordesign so verglichen mit dem Arm Cortex-A9 eine 40 % höhere Rechenleistung erreichen.[17] Beim Big.LITTLE-Prozessing wird ein Cluster bestehend aus Cortex-A12-Cores aus Energiespargründen mit einem Cluster von 1 bis 4 Cortex-A7 zusammen auf einem Chip implementiert, die jeweils abwechselnd je nach Anforderungen der Software an die Rechenleistung diese abarbeiten.[10]

Das Cortex-A12-Design wurde von ARM noch im Jahr 2014 auf das Leistungsniveau des im Februar 2014[18] vorgestellten Cortex-A17 MPCore weiterentwickelt. Im September 2014 gab ARM bekannt, dass der Cortex-A12 nicht mehr weiter als CPU-Design vermarktet wird. Als Ersatz ist der Arm Cortex-A17 MPCore vorgesehen.[19] Der Cortex-A17 soll ARM zufolge rund 60 % schneller sein als der Cortex-A9.[17]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- 40-bit großer physischer Adressraum für bis zu 1 TB RAM, pro Prozess ist jeweils ein 32-bit-Adressraum ansprechbar

- 4 Cores pro Cluster, bis zu 2 Cluster pro Chip mit CoreLink 400 (eine AMBA-4-kohärente Schaltmatrix)

- DSP- und NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz

- TrustZone-Sicherheitserweiterungen

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

Chips

[Bearbeiten | Quelltext bearbeiten]- Rockchip RK3288

- profichip® TRITON[20]

Arm Cortex-A72

[Bearbeiten | Quelltext bearbeiten]

Der 2015 vorgestellte Arm Cortex-A72 MPCore ist wie der A57 ein 64-bit-Multicore-Prozessor mit bis zu vier Cache-kohärenten Cortex-A72-Cores, die jeweils den Armv8-Befehlssatz implementieren. Es handelt sich um ein Dreiwege-superskalares Out-of-Order-Design mit einer 15-stufigen Pipeline. Laut ARM liefert der A72 bei gleicher Taktrate eine „bis zu 50 % höhere Rechenleistung“ als der A57 und besitzt jeweils 48/32 kB L1-Cache für Befehle bzw. Daten sowie einen 512 kB bis 2 MB großen L2-Cache.[21] Der Ziel-Fertigungsprozess soll 16-nm-FinFET von TSMC werden, in welchem Taktfrequenzen von bis zu 2,3 GHz erreicht werden; den theoretischen Maximaltakt gibt ARM mit 2,5 GHz an. Beim Big.LITTLE-Prozessing wird ein Cluster, bestehend aus Cortex-A72-Cores, aus Energiespargründen mit einem „Cluster“ von ein bis vier Cortex-A53 zusammen auf einem Chip implementiert, die jeweils abwechselnd je nach Anforderungen der Software an die Rechenleistung diese abarbeiten. Es ist zu beachten, dass bei der Kalkulation der Rechenleistung im Vergleich zum A57 ein 16-nm-FinFET-Prozess angenommen wird, während die Zahlen für den A57 vom 20-nm-Prozess stammen. Ein erheblicher Teil der Steigerung wird daher rein fertigungstechnisch durch das Mooresche Gesetz erzielt.[22] Die Basis für das Neudesign stellte der Cortex-A57 dar, das in zahlreichen Blöcken optimiert wird, so bei der Sprungvorhersage, den Latenzzeiten bei Gleitkommaoperationen und bei der Cache-Verwaltung. Der Flächenbedarf sank durch die 28-nm-Fertigung von 3,6 mm² (A57) auf 3,3 mm².[23]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.0-A

- 40-bit großer physischer Adressraum für bis zu 1 TB RAM, pro Prozess ist jeweils ein 32-bit-Adressraum ansprechbar

- 4 Cores pro Cluster, bis zu 2 Cluster pro Chip mit CoreLink 500 (eine AMBA-4-kohärente Schaltmatrix, AMBA-5 CHI wird unterstützt)

- DSP- und NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz

- TrustZone-Sicherheitserweiterungen

- Unterstützung von Jazelle DBX für die Ausführung von Java-Code

- Jazelle RCT

- Hardware-Verschlüsselung (AES, SHA-1, SHA-256)[24] optional

Chips

[Bearbeiten | Quelltext bearbeiten]Die System-on-Chips (SoC) mit implementierten Cortex-A72-Cores umfassen u. a.:

- Broadcom BCM2711 (Raspberry Pi 4 Model B; der Arbeitsspeicher befindet sich auf einem eigenen Chip statt auf dem SoC)

- HiSilicon Kirin 950, 955

- NXP i.MX8QM

- Mediatek MT6797(T), MT8173(C), MT8176

- Qualcomm Snapdragon 650, 652, 653

- Rockchip RK3399

- Samsung Exynos 7650

Arm Cortex-A73

[Bearbeiten | Quelltext bearbeiten]Der 2016 vorgestellte Arm Cortex-A73 MPCore ist ein 64-bit-Multicore-Prozessor mit bis zu vier Cortex-A73-Cores, welche jeweils den Armv8-Befehlssatz implementieren. Dabei ist das Core-Design an das des Cortex-A17 angelehnt und gehört nicht zur A15/A57/A72 Entwicklungsreihe. Es handelt sich um ein 2-Wege-superskalares Out-of-Order-Design mit einer 11-stufigen Pipeline, der L1-Cache besitzt 64 kB für Befehle und 32 kB oder 64 kB für Daten. Auf den gemeinsamen L2-Cache (256 kB bis 8 MB) können alle Cores im Cluster gleichzeitig zugreifen. ARM gibt den Takt mit 2,8 GHz an, ein Cluster mit vier Cores, 64 kB/64 kB L1- und 2 MB L2-Cache soll in TSMCs 10FF implementiert ca. 5 mm² groß sein.[25]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.0-A

- 4 Cores pro Cluster (AMBA-4 AXI4 oder ACE wird unterstützt)

- DSP- und NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz

- TrustZone-Sicherheitserweiterungen

Chips

[Bearbeiten | Quelltext bearbeiten]- HiSilicon Kirin 710, 970

- Mediatek MT6799

- Amlogic S905

Arm Cortex-A55

[Bearbeiten | Quelltext bearbeiten]Der 2017 vorgestellte Arm Cortex-A55 MPCore, Nachfolger des Cortex-A53, ist ein 64-bit-Multicore-Prozessor mit bis zu 8 Cortex-A55-Cores, die in einem DynamIQ-Cluster angeordnet sind und implementiert eine Armv8.2-Architektur. Es handelt sich um ein Dual-Decode/Dual-Issue-In-Order-Design, die Integer-Pipeline-Länge beträgt wie beim Cortex-A53 8 Stufen, die NEON/FP-Pipeline 10 Stufen (NEON/FP ist noch immer optional). Statt einer Load-/Store-Unit besitzt der Cortex-A55 nun je eine getrennte Load- und Store-Unit. Ein Core besitzt jeweils einen 16 KiB bis 64 KiB L1-Cache für Befehle und einen für Daten sowie einen optionalen privaten L2-Cache (64 KiB, 128 KiB oder 256 KiB). Über die neu eingeführte DynamIQ Shared Unit kann auf einen optionalen gemeinsamen L3-Cache (1 MiB, 2 MiB oder 4 MiB) zugegriffen werden.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.2-A

- Bis zu 8 A55-Cores pro DynamIQ-Cluster, 4-7 A55-Cores in Kombination mit Cortex-A75 bis -A78 (diese jeweils max. 4)

- NEON-SIMD-Erweiterungen

- VFPv4-Gleitkommaeinheit

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz (nur AArch32)

- TrustZone-Sicherheitserweiterungen

Chips

[Bearbeiten | Quelltext bearbeiten]- HiSilicon Kirin 810, 820, 980, 985, 990

Arm Cortex-A75

[Bearbeiten | Quelltext bearbeiten]Der 2017 vorgestellte Arm Cortex-A75 MPCore, Nachfolger des Cortex-A73, ist ein 64-bit-Multicore-Prozessor mit bis zu 4 Cortex-A75-Cores, die in einem DynamIQ-Cluster angeordnet sind und implementiert eine Armv8.2-Architektur. Es handelt sich um ein 3-Decode/6-Issue-Out-of-Order-Design, die Integer-Pipeline-Länge beträgt wie beim Cortex-A73 11 Stufen; alle Einheiten haben nun eigene, vergrößerte Warteschlangen. Für NEON/FP wurde eine Store-Unit hinzugefügt, die Pipeline-Länge beträgt nun 13 Stufen statt 12. Ein Core besitzt jeweils einen 64 KiB L1-Cache für Befehle und Daten sowie einen privaten 256 KiB oder 512 KiB L2-Cache. Über die neu eingeführte DynamIQ Shared Unit kann auf einen optionalen gemeinsamen L3-Cache (1 MiB, 2 MiB oder 4 MiB) zugegriffen werden.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.2-A

- Cache-Organisation:

- L1: Daten 8-64 KiB, Instruktionen 8-64 KiB,

- L2: 256/512 KiB je Kern,

- L3: über die DynamIQ Shared Unit: bis 4 MiB je Cluster.

- Es können bis zu 3 Instruktionen/Takt dekodiert und 6 dispatched werden.

- 2 Integer-Units.

- Beide NEON-SIMD-Units sind nun in 128-bit-Breite ausgeführt.

- VFPv4-Gleitkommaeinheit

- 2 LD/ST-Units, 1 NEON-ST-Unit.

- Bis zu 8 Cores pro DynamIQ-Cluster (aber nur max. 4 Cortex-A75) in Kombination mit Cortex-A55

- Unterstützung von Hardware-Virtualisierung

- Thumb-2-Befehlssatz (nur AArch32)

- TrustZone-Sicherheitserweiterungen

Arm Cortex-A76

[Bearbeiten | Quelltext bearbeiten]Im Mai 2018 wurde der Arm Cortex-A76 als Nachfolger des A75 vorgestellt[26]. Die Mikroarchitektur basiert wie beim Vorgänger auf dem Armv8.2-Befehlssatz, die Prozessor-Baupläne / IP sind für 10-nm- und 7-nm-Lithografie-Prozesse erhältlich, als maximale Taktrate wird 3,0 GHz angegeben (7 nm)[27].

Als erstes SoC mit A76 erscheint der Kirin 980 von HiSilicon in 7-nm-Fertigungstechnik: je zwei A76-Kerne arbeiten hier mit unterschiedlichen Taktfrequenzen zusammen mit vier A55-Kernen in einem 2+2+4 DynamIQ-Cluster. Das erste Smartphone mit Kirin 980 ist Ende 2018 das Huawei Mate 20.

Für sicherheitskritische Automotiveanwendungen führte ARM im September 2018 die Version Cortex-A76AE ein.[28] Der A76-Core diente auch als Grundlage des für den Servermarkt entwickelten und im Februar 2019 vorgestellten Neoverse N1.[29]

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.2-A

- Cache-Organisation wie bisher:

- L1: Daten 8-64 KiB, Instruktionen 8-64 KiB,

- L2: 256/512 KiB je Kern,

- L3: über die DynamIQ Shared Unit: bis 4 MiB je Cluster.

- Es können bis zu 4 (A75: 3) Instruktionen/Takt dekodiert und 8 (A75: 6) dispatched werden, die IPC Werte können bis zu 30 % höher als beim Vorgänger A75 liegen.

- Die Anzahl der Integer-Units wurde auf 3 (A75: 2) erhöht, 2 sind zu einfachen und 1 zu komplexen Aufgaben fähig.

- Beide NEON-SIMD-Units sind in 128-bit-Breite ausgeführt.

- 2 LD/ST-Units, die NEON-ST-Unit entfällt.

- Bis zu 8 Cores pro DynamIQ-Cluster (aber nur max. 4 Cortex-A76) in Kombination mit Cortex-A55.

- ARM gibt gegenüber dem A75 in 10 nm entweder 40 % mehr Rechenleistung oder 50 % weniger Energieverbrauch an.

- Es wird eine nicht näher erläuterte „höhere AI / ML“ – Performance angegeben.

Chips

[Bearbeiten | Quelltext bearbeiten]- HiSilicon Kirin 810, 820, 980, 985, 990

- Qualcomm Snapdragon 855, 855+, 860

- Samsung Exynos 990

- Broadcom BCM2712

Arm Cortex-A65AE

[Bearbeiten | Quelltext bearbeiten]Im Dezember 2018 wurde der Arm Cortex-A65AE vorgestellt[30]. Die Mikroarchitektur basiert auf dem Armv8.2-Befehlssatz, es handelt sich um den ersten ARM-Core, der SMT unterstützt, und er ist wie der Cortex-A76AE für "Automotive"-Anwendungen gedacht. Es können bis zu 8 Cores in einem DynamIQ-Cluster untergebracht werden.[31]

Arm Cortex-A77

[Bearbeiten | Quelltext bearbeiten]Im Mai 2019 wurde der Arm Cortex-A77 als Nachfolger des A76 vorgestellt[32]. Die Mikroarchitektur basiert wie beim Vorgänger auf dem Armv8.2-Befehlssatz, die Prozessor-Baupläne / IP sind für 7-nm-Lithografie-Prozesse erhältlich, als maximale Taktrate wird 3,0 GHz angegeben[33].

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.2-A

- Cache-Organisation:

- L1: Daten 64 KiB, Instruktionen 64 KiB,

- L2: 256/512 KiB je Kern,

- L3: optional über die DynamIQ Shared Unit: 512 KiB bis 4 MiB je Cluster.

- Erstmals wurde von ARM ein Macro-Ops-Cache mit 1536 Einträgen eingeführt; es können 6 MOps/Takt parallel zum Decoder abgerufen werden.

- Der Reorder-Buffer wurde auf 160 Einträge erweitert (A76: 128).

- Es können bis zu 4 Instruktionen/Takt dekodiert und 10 (A76: 8) dispatcht werden.

- Die Anzahl der Integer-Units wurde auf 4 (A76: 3) erhöht, es ist weiterhin 1 Unit zu komplexen Aufgaben fähig.

- Die Anzahl der Branch-Units wurde auf 2 (A76: 1) erhöht.

- 2 NEON-SIMD-Units 128-bit.

- 2 LD/ST-Units, Erweiterung um 2 ST Data.

- Bis zu 8 Cores pro DynamIQ-Cluster (aber nur max. 4 Cortex-A77) in Kombination mit Cortex-A55.

- ARM gibt gegenüber dem A76 20 % mehr Rechenleistung an.

Chips

[Bearbeiten | Quelltext bearbeiten]- Qualcomm Snapdragon 865, 865+, 870

- MediaTek Dimensity 1000+

Arm Cortex-A78

[Bearbeiten | Quelltext bearbeiten]Im Mai 2020 wurde der Arm Cortex-A78 als Nachfolger des A77 vorgestellt[34]. Die Mikroarchitektur basiert wie beim Vorgänger auf dem Armv8.2-Befehlssatz, die Prozessor-Baupläne / IP sind für 5-nm-Lithografie-Prozesse erhältlich, als maximale Taktrate wird 3,0 GHz angegeben. Der Entwicklungsschwerpunkt lag laut Arm auf der Effizienzsteigerung. Zusammen mit dem Cortex-A78 wurde auch ein auf Leistung ausgelegter Cortex-X1 vorgestellt.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.2-A

- Cache-Organisation:

- L1: Daten 32/64 KiB, Instruktionen 32/64 KiB,

- L2: 256/512 KiB je Kern,

- L3: optional über die DynamIQ Shared Unit: 512 KiB bis 4 MiB je Cluster.

- MOps-Cache mit 1536 Einträgen, 6 MOps/Takt.

- Reorder-Buffer mit 160 Einträgen

- Es können bis zu 4 Instruktionen/Takt dekodiert und 12 (A77: 10) dispatcht werden.

- Die Anzahl der Integer-Units beträgt 4, es sind nun aber 2 Units zu komplexen Aufgaben fähig (A77: 1).

- 2 Branch-Units.

- 2 NEON-SIMD-Units 128-bit.

- 2 LD/ST-Units und 2 ST Data, es wurde 1 LD-Unit neu hinzugefügt.

- Bis zu 8 Cores pro DynamIQ-Cluster (aber nur max. 4 Cortex-A78) in Kombination mit Cortex-A55. Von der Variante Cortex-A78C können hingegen bis zu 8 pro DynamIQ-Cluster verbaut werden, der L3-Cache kann dann bis zu 8 MiB groß sein.

- ARM gibt gegenüber dem A77 20 % mehr Rechenleistung in einer Mobil-Umgebung an.

Chips

[Bearbeiten | Quelltext bearbeiten]- MediaTek Dimensity 1200

- Qualcomm Snapdragon 888, 8cx Gen 3

- Samsung Exynos 2100

Arm Cortex-A510

[Bearbeiten | Quelltext bearbeiten]Im Mai 2021 wurde der Arm Cortex-A510 als Nachfolger des A55 vorgestellt[35]. Die Mikroarchitektur basiert nun erstmals auf dem Armv9.0-Befehlssatz; neu ist dabei auch die Verwendung von SVE2-SIMD-Einheiten bei voller NEON-Kompatibilität. Der Entwicklungsschwerpunkt lag laut Arm weiterhin auf der Effizienzsteigerung. Zusammen mit dem Cortex-A510 wurde auch ein auf Leistung ausgelegter Cortex-X2 und ein mehr auf Effizienz ausgeleger Cortex-A710 vorgestellt, sowie eine neue DynamIQ Shared Unit DSU-110.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv9.0-A

- Der A510 unterstützt nur noch AArch64.

- In-Order-Design

- Cache-Organisation:

- L1: Daten 32/64 KiB, Instruktionen 32/64 KiB,

- L2: 0–512 KiB,

- L3: optional über die DynamIQ Shared Unit: 512 KiB bis 8 MiB je Cluster.

- 128-bit Fetch

- Es können bis zu 3 Instruktionen/Takt (A55: 2) dekodiert und weiterverarbeitet werden.

- 4 Integer-Units (A55: 2), es ist 1 Unit zu komplexen Aufgaben fähig.

- 1 Branch-Unit.

- 2 SVE2-Units, die in 64-bit- oder 128-bit-Breite ausgeführt sein können (Registerbreite ist immer 128-bit).

- 1 LD/ST-Unit, 1 LD-Unit (A55: 1 LD/1 ST).

Zwei Cortex-A510 können zu einem Complex zusammengefasst werden. Sie teilen sich dann den L2-Cache inklusive des L2-TLB und die SVE2-Units. Bei letzteren verwaltet ein eigener Arbiter die Anforderungen der beiden A510-Cores, die ansonsten unabhängig voneinander bleiben. Ein A510-Complex belegt in der DSU-110 nur einen Node.

Chips

[Bearbeiten | Quelltext bearbeiten]- MediaTek Dimensity 9000

- Qualcomm Snapdragon 8 Gen1, 8+ Gen1

- Samsung Exynos 2200

Arm Cortex-A710

[Bearbeiten | Quelltext bearbeiten]Im Mai 2021 wurde der Arm Cortex-A710 als Nachfolger des A78 vorgestellt[36]. Die Mikroarchitektur basiert nun erstmals auf dem Armv9.0-Befehlssatz; neu ist dabei auch die Verwendung von SVE2-SIMD-Einheiten bei voller NEON-Kompatibilität. Der Entwicklungsschwerpunkt lag laut Arm weiterhin auf der Effizienzsteigerung. Zusammen mit dem Cortex-A710 wurde auch ein auf Leistung ausgelegter Cortex-X2 und ein auf Effizienz ausgeleger Cortex-A510 vorgestellt, sowie eine neue DynamIQ Shared Unit DSU-110. Der A710-Core diente auch als Grundlage des für den Servermarkt entwickelten und im April 2021 vorgestellten Neoverse N2.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv9.0-A

- Der A710 unterstützt AArch32 nur noch in EL0.

- Cache-Organisation:

- L1: Daten 32/64 KiB, Instruktionen 32/64 KiB,

- L2: 256/512 KiB je Kern,

- L3: optional über die DynamIQ Shared Unit: 512 KiB bis 8 MiB je Cluster.

- MOps-Cache mit 1536 Einträgen, 5 MOps/Takt (A78: 6).

- BTB und GHB wurden verdoppelt, der L1I-TLB um 50 % vergrößert.

- Reorder-Buffer mit 160 Einträgen

- Es können bis zu 4 Instruktionen/Takt dekodiert und 10 (A78: 12) dispatcht werden.

- Die Pipeline konnte (im Dispatch) um eine Stufe auf 10 verkürzt werden.

- 4 Integer-Units, es sind 2 Units zu komplexen Aufgaben fähig.

- 2 Branch-Units.

- Die beiden SVE2-Units sind in 128-bit-Breite ausgeführt.

- 2 LD/ST-Units, 1 LD-Unit und 2 ST Data.

- Bis zu 8 Cores pro DynamIQ-Cluster (aber nur max. 4 Cortex-A710).

- ARM gibt gegenüber dem A78 10 %, bei ML-Anwendungen 100 % mehr Rechenleistung an.

Arm Cortex-A715

[Bearbeiten | Quelltext bearbeiten]Im Juni 2022 wurde der Arm Cortex-A715 als Nachfolger des A710 vorgestellt[37]. Die Mikroarchitektur basiert auf dem Armv9.0-Befehlssatz. Der Entwicklungsschwerpunkt lag laut Arm noch stärker auf der Effizienzsteigerung als schon beim A710. Zusammen mit dem Cortex-A715 wurde auch ein auf Leistung ausgelegter Cortex-X3 vorgestellt und der Cortex-A510 sowie die DynamIQ Shared Unit DSU-110 wurden aufgefrischt.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv9.0-A

- Der A715 unterstützt nur noch AArch64.

- Cache-Organisation:

- L1: Daten 32/64 KiB, Instruktionen 32/64 KiB,

- L2: 128/256/512 KiB je Kern, der L2 TLB wurde um 50 % vergrößert,

- L3: optional über die DynamIQ Shared Unit: 256 KiB bis 16 MiB je Cluster.

- Der MOps-Cache wurde entfernt.

- Reorder-Buffer mit 192 Einträgen

- Die Sprungvorhersage wurde ausgeweitet.

- Es können nun bis zu 5 Instruktionen/Takt dekodiert (A710: 4) und 5 MOPS dispatcht werden.

- 4 Integer-Units, es sind 2 Units zu komplexen Aufgaben fähig.

- 2 Branch-Units.

- Die beiden SVE2-Units sind in 128-bit-Breite ausgeführt.

- 2 LD/ST-Units und 2 ST Data.

- Bis zu 12 Cores pro DynamIQ-Cluster.

Arm Cortex-X1

[Bearbeiten | Quelltext bearbeiten]Im Mai 2020 wurde zusammen mit dem Cortex-A78 der Cortex-X1 vorgestellt[34]. Die Mikroarchitektur basiert auf dem Armv8.2-Befehlssatz, die Prozessor-Baupläne / IP sind für 5-nm-Lithografie-Prozesse erhältlich, als maximale Taktrate wird 3,0 GHz angegeben. Der Entwicklungsschwerpunkt lag laut Arm auf der Performancesteigerung und verspricht bis zu 30 % mehr Leistung im Vergleich zu einem Cortex-A77. (Weiter Infos: siehe Cortex-A78)

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv8.2-A

- Cache-Organisation:

- L1: Daten 64 KiB, Instruktionen 64 KiB,

- L2: 512/1024 KiB je Kern,

- L3: optional über die DynamIQ Shared Unit: 2 bis 8 MiB je Cluster.

- MOps-Cache mit 3072 Einträgen, 8 MOps/Takt.

- ROB (244) und BTB (96) wurden gegenüber dem A78 deutlich vergrößert.

- Es können bis zu 5 Instruktionen/Takt dekodiert und 16 (8 MOPS) dispatcht werden.

- 4 Integer-Units, es sind 2 Units zu komplexen Aufgaben fähig.

- 2 Branch-Units.

- Die vier NEON-Units sind in 128-bit-Breite ausgeführt.

- 2 LD/ST-Units, 1 LD-Unit und 2 ST Data.

Chips

[Bearbeiten | Quelltext bearbeiten]- Qualcomm Snapdragon 888, 8cx Gen3

- Samsung Exynos 2100

Arm Cortex-X2

[Bearbeiten | Quelltext bearbeiten]Im Mai 2021 wurde zusammen mit dem Cortex-A710 der Cortex-X2 Nachfolger der Cortex-X1 vorgestellt[36]. Die Mikroarchitektur basiert nun erstmals auf dem Armv9.0-Befehlssatz. Der Entwicklungsschwerpunkt lag laut Arm weiterhin auf der Performancesteigerung und verspricht bis zu 16 % mehr Leistung als der Cortex-X1. Zusammen mit dem Cortex-X2 wurde auch der Cortex-A710 und ein auf Effizienz ausgelegter Cortex-A510 vorgestellt.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv9.0-A

- Der X2 unterstützt nur AArch64.

- Cache-Organisation:

- L1: Daten 64 KiB, Instruktionen 64 KiB,

- L2: 512/1024 KiB je Kern,

- L3: optional über die DynamIQ 110 Shared Unit: 2 bis 8 MiB je Cluster.

- MOps-Cache mit 3072 Einträgen, 8 MOps/Takt.

- ROB (288) und BTB (128) wurden vergrößert.

- Es können bis zu 5 Instruktionen/Takt dekodiert und 16 (8 MOPS) dispatcht werden.

- 4 Integer-Units, es sind 2 Units zu komplexen Aufgaben fähig.

- 2 Branch-Units.

- Die vier SVE2-Units sind in 128-bit-Breite ausgeführt.

- 2 LD/ST-Units, 1 LD-Unit und 2 ST Data.

Chips

[Bearbeiten | Quelltext bearbeiten]- Qualcomm Snapdragon 8 Gen1

- MediaTek Dimensity 9000

- Samsung Exynos 2200

Arm Cortex-X3

[Bearbeiten | Quelltext bearbeiten]Im Mai 2022 wurde zusammen mit dem Cortex-A715 der Cortex-X3 als Nachfolger des Cortex-X2 vorgestellt. Die Mikroarchitektur basiert auf dem Armv9.0-Befehlssatz.

Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- ARMv9.0-A

- Der X3 unterstützt nur AArch64.

- Cache-Organisation:

- L1: Daten 64 KiB, Instruktionen 64 KiB,

- L2: 512/1024 KiB je Kern,

- L3: optional über die DynamIQ 110 Shared Unit: 2 bis 8 MiB je Cluster.

- Der MOps-Cache wurde auf 1536 Einträge verkleinert, 8 MOps/Takt.

- ROB (320) und BTB (192) wurden vergrößert.

- Es können nun bis zu 6 Instruktionen/Takt dekodiert und 16 (8 MOps) dispatcht werden.

- 6 Integer-Units, es sind 2 Units zu komplexen Aufgaben fähig.

- 2 Branch-Units.

- Die vier SVE2-Units sind in 128-bit-Breite ausgeführt.

- 2 LD/ST-Units, 1 LD-Unit und 2 ST Data.

Chips

[Bearbeiten | Quelltext bearbeiten]- Qualcomm Snapdragon 8 Gen3

- MediaTek Dimensity 9200

Lizenznehmer und Produkte (Armv7-A)

[Bearbeiten | Quelltext bearbeiten]| Allwinner | AMLogic | Apple | Broadcom | Freescale | HiSilicon | MediaTek | Nvidia | Rockchip | Samsung | ST-Ericsson | TI | Qualcomm | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Cortex-A8 | A10, A13 |

A4 | i.MX5x | RK2918 | Exynos 3 | OMAP3 AM335x |

|||||||

| Cortex-A9 | AML7366-M und AML8726- (M, M3L, M6, MX) |

A5 | BCM11311 | verschiedene Modelle aus der i.MX6-Serie |

K3V2 | MT6575, MT6577, MT8317T, MT8377 |

Tegra 2, Tegra 3, Tegra 4i |

RK3066, RK3188, RK3168 |

Exynos 4 | Nova U8500 | OMAP4 | ||

| Cortex-A7 | A20, A31 |

BCM2836 | i.MX6ULL, i.MX6UltraLite, i.MX7Dual family |

MT5807, MT6517, MT6572, MT6582(M), MT6589(T), MT6592, MT8121, MT8125, MT8127, MT8312, MT8389 |

STM32MP1 | ||||||||

| Cortex-A12 | RK32XX | ||||||||||||

| Cortex-A15 | Tegra 4, Tegra K1 |

Exynos 5 Dual, Quad |

Nova A9600 | OMAP5 | |||||||||

| Cortex-A17 | MT5861, MT5890 | ||||||||||||

| big.LITTLE A7 + A12 |

|||||||||||||

| big.LITTLE A7 + A15 |

K3V3 | MT8135 | Exynos 5 Octa |

||||||||||

| big.LITTLE A7 + A17 |

MT5595, MT6595(M/T) | ||||||||||||

| Big.LITTLE

A55 + A76 |

Dimensity 820

(MT6875) |

Exynos 990

(S5E9830) |

Snapdragon 860

(SM8150-AC) | ||||||||||

| Prime.big.LITTLE

A5 5+ A78 + X1 |

Exynos 2100

(S5E9840) |

Snapdragon 888

(SM8350) | |||||||||||

| Prime.big.LITTLE

A510 + A710 + X2 |

Exynos 2200 | Snapdragon 8 Gen1

(SM8475) |

Siehe auch

[Bearbeiten | Quelltext bearbeiten]- Arm-Architektur

- Kryo ARM-CPU-Modellreihe

Weblinks

[Bearbeiten | Quelltext bearbeiten]- Cortex-A Series – High Performance Application Processing

- Produktbeschreibung des Arm Cortex-A5 (englisch)

- Produktbeschreibung des Arm Cortex-A7 (englisch)

- Produktbeschreibung des Arm Cortex-A8 (englisch)

- Produktbeschreibung des Arm Cortex-A9 (englisch)

- Produktbeschreibung des Arm Cortex-A15 (englisch)

- Produktbeschreibung des Arm Cortex-A17 (englisch)

- Produktbeschreibung des Arm Cortex-A32 (englisch)

- Produktbeschreibung des Arm Cortex-A34 (englisch)

- Produktbeschreibung des Arm Cortex-A35 (englisch)

- Produktbeschreibung des Arm Cortex-A53 (englisch)

- Produktbeschreibung des Arm Cortex-A55 (englisch)

- Produktbeschreibung des Arm Cortex-A57 (englisch)

- Produktbeschreibung des Arm Cortex-A72 (englisch)

- Produktbeschreibung des Arm Cortex-A73 (englisch)

- Produktbeschreibung des Arm Cortex-A75 (englisch)

- Produktbeschreibung des Arm Cortex-A76 (englisch)

- Produktbeschreibung des Arm Cortex-A77 (englisch)

- Produktbeschreibung des Arm Cortex-A78 (englisch)

- Produktbeschreibung des Arm Cortex-A510 (englisch)

- Produktbeschreibung des Arm Cortex-A710 (englisch)

- Produktbeschreibung des Arm Cortex-A715 (englisch)

- https://www.qualcomm.com/products/application/smartphones/snapdragon-8-series-mobile-platforms/snapdragon-855-plus-and-860-mobile-platform#Overview

- https://wikimovel.com/index.php/Samsung_Exynos_990

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ ARM: Pressemitteilung vom 4. Oktober 2005.

- ↑ a b c Frank Riemenschneider: Cortex-A5 für Mikrocontroller- und Multiprozessing-Anwendungen. In: Elektroniknet.de, 4. Juni 2010. ( vom 23. September 2015 im Internet Archive)

- ↑ a b ARM: ARM Unveils Cortex-A9 Processors For Scalable Performance and Low-Power Designs, Pressemitteilung vom 3. Oktober 2007.

- ↑ ARM: Processor variants ( vom 21. August 2017 im Internet Archive) In: Arm Cortex-A9 Technical Reference Manual r4p1, 2016.

- ↑ Cortex-A9 Processor bei ARM.com, abgerufen am 20. August 2013.

- ↑ Benjamin Benz: ARM: Nachwuchs für die die Cortex-A-Familie. In: Heise online. 22. Oktober 2009. Abgerufen am 30. Januar 2022.

- ↑ YASKAWA: ANTAIOS, Real-time Ethernet Communication Controller. (PDF) Archiviert vom (nicht mehr online verfügbar) am 28. März 2022; abgerufen am 19. März 2021. Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis.

- ↑ ARM: ARM Unveils Cortex-A15 MPCore Processor to Dramatically Accelerate Capabilities of Mobile, Consumer and Infrastructure Applications, Pressemitteilung vom 8. September 2010.

- ↑ Frank Riemenschneider: Cortex-A15 zielt auf Kommunikations- und Server-Markt. In: Elektroniknet.de, 10. März 2011. ( vom 23. September 2015 im Internet Archive)

- ↑ a b c d e f Frank Riemenschneider: ARM paart Cortex-A7 und Cortex-A15. In: Elektroniknet.de, 13. Juni 2012. ( vom 23. September 2015 im Internet Archive)

- ↑ Christof Windeck: ARM stellt neuen SoC-Prozessorkern Cortex-A7 vor. In: Heise online. 20. Oktober 2011. Abgerufen am 30. Januar 2022..

- ↑ ARM: Cortex-A7 MPCore Revision: r0p3 – Technical Reference Manual, S. 6–2, 7-2.

- ↑ The MediaTek MT6592 chipset benchmark test leaked online In: GIZMOCHINA, 17. Oktober 2013.

- ↑ MediaTek Helio P25 Specifications In: mediatek.com.

- ↑ a b Frank Riemenschneider: ARM enthüllt neue 64-bit-Cores. In: Elektroniknet.de, 30. Oktober 2012. ( vom 4. März 2016 im Internet Archive)

- ↑ Frank Riemenschneider: ARM Cortex-A12: Der Nachfolger für den Cortex-A9 steht bereit. In: Elektroniknet.de, 13. August 2013. ( vom 23. September 2015 im Internet Archive)

- ↑ a b Benjamin Benz: Neuer ARM-Kern für Mittelklasse-Smartphones. In: Heise online. 11. Februar 2014. Abgerufen am 30. Januar 2022..

- ↑ ARM: Cortex-A17 and an enhanced suite of IP targeted at the mid-range mobile market., 13. Februar 2014.

- ↑ ARM: ARM Cortex-A17 / Cortex-A12 processor update., 30. September 2014.

- ↑ YASKAWA: TRITON, flexibler PLC, Motion- und Gigabit-Ethernet-Kommunikationscontroller mit integriertem Backplane-Master. (PDF) YASKAWA Europe GmbH, archiviert vom (nicht mehr online verfügbar) am 16. Januar 2023; abgerufen am 19. März 2021. Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis.

- ↑ ARM: Cortex-A72 Processor.

- ↑ Lars Bube: ARM Cortex-A72 soll neue Messlatte setzen. In: connect professional. 13. Februar 2015, abgerufen am 6. November 2023.

- ↑ Frank Riemenschneider: ARM-Chefarchitekt stellt Cortex-A72-Details vor. ( vom 1. Mai 2015 im Webarchiv archive.today), Artikel bei Elektroniknet.de vom 29. April 2015.

- ↑ Security – the Fundamental Element in Next-Gen Networks. Abgerufen am 17. Dezember 2019 (englisch).

- ↑ Andrei Frumusanu: The ARM Cortex A73 – Artemis Unveiled. Artikel bei AnandTech.com vom 29. Mai 2016.

- ↑ https://www.anandtech.com/show/13614/arm-delivers-on-cortex-a76-promises

- ↑ https://developer.arm.com/products/processors/cortex-a/cortex-a76

- ↑ https://developer.arm.com/ip-products/processors/cortex-a/cortex-a76ae

- ↑ https://www.anandtech.com/show/13959/arm-announces-neoverse-n1-platform

- ↑ https://www.anandtech.com/show/13727/arm-announces-cortex65ae-for-automotive-first-smt-cpu-core

- ↑ https://developer.arm.com/ip-products/processors/cortex-a/cortex-a65ae

- ↑ https://www.anandtech.com/show/14384/arm-announces-cortexa77-cpu-ip

- ↑ https://developer.arm.com/ip-products/processors/cortex-a/cortex-a77

- ↑ a b https://www.anandtech.com/show/15813/arm-cortex-a78-cortex-x1-cpu-ip-diverging

- ↑ https://www.anandtech.com/show/16693/arm-announces-mobile-armv9-cpu-microarchitectures-cortexx2-cortexa710-cortexa510

- ↑ a b https://www.anandtech.com/show/16693/arm-announces-mobile-armv9-cpu-microarchitectures-cortexx2-cortexa710-cortexa510

- ↑ https://fuse.wikichip.org/news/6853/arm-introduces-the-cortex-a715/